# Single Chip micro Mote $SC\mu M$ -3C User Guide

Lydia Lee, Fil Maksimovic, Alex Moreno, Kris Pister, Titan Yuan, Brad Wheeler

Last Compiled October 1, 2019

# Contents

| 1        | Intro                              | 5  |

|----------|------------------------------------|----|

| <b>2</b> | Quick Start - Hello World          | 6  |

| 3        | Where To Go For Resources and Help | 6  |

|          | 3.1 GitHub                         | 7  |

|          | 3.2 Box                            | 7  |

|          | 3.3 BWRC Repo                      | 7  |

|          | 3.4 OpenWSN Repo                   | 7  |

|          | 3.5 JIRA                           | 7  |

|          | 3.6 EECS Repo                      | 7  |

| 4        | Chip Overview                      | 8  |

|          | 4.1 Analog Scan Chain              | 9  |

|          | 4.2 Memory Mapped Registers        | 10 |

|          | 4.3 Pads                           | 10 |

|          | 4.4 Voltage Domains                | 12 |

| <b>5</b> | PCB Overview                       | 12 |

| 6        | Electrical Specification           | 14 |

| <b>7</b> | Bootloading                                                                                                | <b>14</b> |

|----------|------------------------------------------------------------------------------------------------------------|-----------|

|          | 7.1 Optical Bootloading                                                                                    | 14        |

|          | 7.2 3-Wire Bus Bootloading                                                                                 | 16        |

|          | 7.3 Mote Startup $\ldots$ | 16        |

|          | 7.4 Optical Boot Troubleshoot                                                                              | 17        |

| 8        | Misc Optical Bootload Related Items                                                                        | 17        |

|          | 8.1 Optical Data Transfer                                                                                  | 17        |

|          | 8.2 Optical Timing Transfer                                                                                | 18        |

|          | 8.3 Lighthouse Localization Receiver                                                                       | 19        |

|          | 8.4 Future Feature Idea: Hardware IDs & Calibration Data                                                   | 19        |

|          | 8.5 Future Feature Idea: RF Bootloader                                                                     | 19        |

| 9        | GPIO                                                                                                       | 19        |

| 10       | ) Interrupts                                                                                               | 22        |

| 11       | l UART                                                                                                     | 23        |

| 12       | 2 SPI                                                                                                      | <b>24</b> |

| 13       | 3 Clock Configuration                                                                                      | <b>24</b> |

|          | 4 Frequency Counters                                                                                       | <b>24</b> |

| 14       | Frequency Counters                                                                                         | <b>24</b> |

| 15       | 5 Timers                                                                                                   | <b>24</b> |

| 16       | 5 LO, PA, and Divider Hardware Details                                                                     | <b>25</b> |

|          | 16.1 Analog Scan Chain                                                                                     | 25        |

|          | 16.2 Cortex Code                                                                                           | 27        |

|          | 16.3 Common Configurations                                                                                 | 28        |

|          | 16.3.1 Receive Mode (RF only)                                                                              | 28        |

|          | 16.3.2 Transmit Mode - 802.15.4                                                                            | 29        |

|          | 16.3.3 Transmit Mode - BLE $\ldots$                                                                        | 29        |

| 17       | 7 RF Receiver Analog Scan Chain                                                                            | 31        |

|          | 17.1 Mixer Bias                                                                                            | 31        |

|          | 17.2 Transimpedance Amplifiers                                                                             | 32        |

|          | 17.3 Gain Control                                                                                          | 32        |

|           | 17.4 | Filters                                                                             | 33 |

|-----------|------|-------------------------------------------------------------------------------------|----|

|           | 17.5 | ADC                                                                                 | 34 |

|           | 17.6 | Clock Generation                                                                    | 36 |

|           |      | LDO and Reset                                                                       | 36 |

|           | 17.8 | Debug Path                                                                          | 37 |

| 18        | Pow  | ver On Control                                                                      | 39 |

|           | 18.1 | Aux Digital LDO                                                                     | 41 |

|           | 18.2 | Power Sequencing                                                                    | 41 |

|           | 18.3 | TX/RX Switching                                                                     | 44 |

| 19        | Digi | ital Baseband                                                                       | 45 |

|           | 19.1 | RSSI                                                                                | 47 |

|           | 19.2 | Link Quality Indicator                                                              | 47 |

|           | 19.3 | Chip Rate Error Estimate                                                            | 47 |

| 20        | Sens | sor ADC                                                                             | 48 |

|           | 20.1 | Hardware                                                                            | 48 |

|           |      | 20.1.1 LDO                                                                          | 50 |

|           |      | 20.1.2 PTAT                                                                         | 50 |

|           |      | 20.1.3 PGA                                                                          | 51 |

|           |      | 20.1.4 ADC                                                                          | 51 |

|           | 20.2 | Initializing Analog Scan Chain                                                      | 51 |

|           | 20.3 | Triggering A Measurement                                                            | 52 |

|           |      | 20.3.1 On-Chip FSM                                                                  | 53 |

|           |      | 20.3.2 GPIO Loopback                                                                | 53 |

|           |      | 20.3.3 External GPI                                                                 | 54 |

|           | 20.4 | Reading the Output                                                                  | 54 |

|           |      | 20.4.1 Memory-Mapped Register                                                       | 54 |

|           |      | 20.4.2 GPO Readout                                                                  | 54 |

|           | 20.5 | Debugging/Known Issues                                                              | 54 |

|           |      | 20.5.1 Supply Bounce $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 54 |

|           |      | 20.5.2 First-Reading 511                                                            | 55 |

|           |      | 20.5.3 MSB "Sticking"                                                               | 55 |

| <b>21</b> | Raw  | v Bit Receive Mode                                                                  | 56 |

| 22 802.15.4 Radio Demo Software   | <b>56</b> |

|-----------------------------------|-----------|

| 22.1 Overview                     | 56        |

| 22.2 CRC Check                    | 57        |

| 22.3 Initialize Analog Scan Chain | 57        |

| 22.4 Optical Calibration          | 57        |

| 22.5 Building a Channel Table     | 57        |

| 22.6 Acquiring Packet Rate        | 59        |

| 22.7 Frequency Management         | 59        |

| 22.8 BSP-like Radio Control       | 60        |

| 22.9 Hard-Wired Radio Connection  | 61        |

|                                   |           |

| 23 Optical Programmer Details     | 61        |

## 1 Intro

The goal of the Single Chip micro Mote project is to develop a complete selfcontained wireless sensor node on a single chip, including sensing, computation, communication, and power, with no external components. SCµM3C is an important step along that path, containing everything needed for sensing, computation, and communication. This includes a 32 bit Cortex M0 processor, 2.4 GHz radio transceiver, and both a temperature sensor and a lighthouse location sensor. With a printed solar cell and battery, SCµM3C would satisfy the project goal. SCµM3C is the product of graduate research over a period of roughly six years by a core group of four students and a postdoc, and an extended group that includes dozens of graduate and undergraduate students and visiting scholars. The academic contributions are featured in three doctoral dissertations [1, 2, 4] and one master's thesis [3], as well as an expanding number of research publications describing the crystalfree approach [**xxx**], circuit design [**xxx**], and applications [**xxx**].

This User Guide is intended as a practical explanation of how to use  $SC\mu M3C$ . Because the chip was designed by students learning new skills and pursuing a research agenda, it has some quirks not found in typical production silicon. There are often optional ways of doing things that were included out of concern that new circuits would not work precisely as designed, and many cases where legacy mechanisms were left in place because there simply was not enough time to fix them. There are also a large number of debugging pads and interfaces. And of course, not everything works.

Because this chip is a research project not a commercial product, the documentation is not as well organized or complete as it might be. Work is in progress to improve that situation. This document attempts to consolidate information useful for operating and debugging on SCM-3C.

For Your Safety: As discussed later in the optical bootloading section, be careful with the optical programmers! They use high intensity infrared nonvisible light which can damage eyes and skin at very short distances or long exposure times. For SCM's Safety: Take precautions against ESD by grounding yourself before handling SCM. If you are applying external connections be sure to adhere to the maximum voltage ratings which differ depending on the pin. Take precautions to avoid scratching the epoxy covering the chip as this can degrade optical programming if the photodiode is obscured.

# 2 Quick Start - Hello World

The TL;DR version of this guide. Each of the following steps are described in detail in this guide and the mentioned references. A high level summary of the steps to get started running code on SCM are:

- Download and install ARM Keil (see [3]).

- Download example software from GitHub (see Section 3.1).

- Download bootloader script from GitHub (see Section 3.1).

- Update bootloader script with COM port and binary file path.

- Obtain a SCM-3C test PCB.

- Obtain an optical programmer PCB and Teensy with correct firmware.

- Plug both boards in via USB and open a COM port to SCM.

- Align the programmer and execute the bootload script.

- SCM should print over UART and toggle its GPIOs.

# 3 Where To Go For Resources and Help

Documentation, code, and source files are located in several different places which are listed below.

## 3.1 GitHub

Software for version 3C is hosted on GitHub or here: https://github.com/ PisterLab/scum-test-code

## 3.2 Box

Bootloader scripts, Teensy bootloader firmware, scripts for utilizing scan chains, and PCB documentation can be found on Box in the uRobots/SCM\_3C folder. Documentation can also be found in this folder. A detailed description of the Cortex-M0 and its associated digital blocks can be found in [3]. The hardware implementation of the radio and optical receivers is detailed in [4]. The RF local oscillator, transmitter, and divider are discussed in [2]. Clocks, POR, and reset logic are discussed in [1]. A useful book describing various aspects of the ARM Cortex-M0 can be found here [5]. Permission to access this folder must be given by someone within the group.

# 3.3 BWRC Repo

The source Verilog and digital synthesis flow used to create the SCM ASIC are located in this repo which is private due to IP restrictions. This repo, the analog portion of the design, and the final GDS reside on BWRC servers.

# 3.4 OpenWSN Repo

The OpenWSN repo which supports SCM can be found here: https://github.com/openwsn-berkeley/openwsn-fw

## 3.5 JIRA

JIRA was used for bug tracking during tapeouts and contains historical details of issues and the status of their resolution: https://openwsn.atlassian. net/projects/SCUM/issues

## 3.6 EECS Repo

Some software still resides in the EECS Repo which was where software was stored at the beginning of the project: repo.eecs.berkeley.edu/git/ projects/pistergroup/singlechip-digital.git

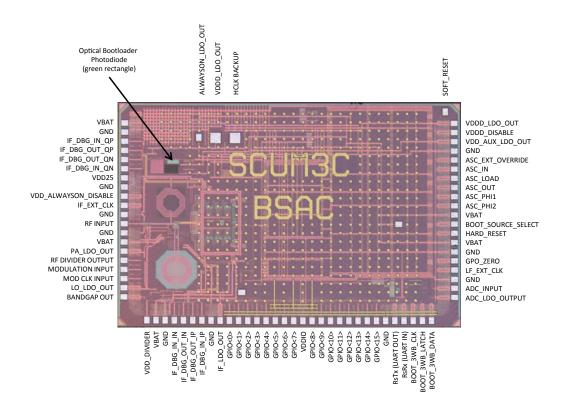

Figure 1: Die photo of SCM-3C with pad labels. Dimensions are  $3\text{mm} \times 2\text{mm} \times 0.3\text{mm}$ .

# 4 Chip Overview

$SC\mu M$ -3C is a  $3x2x0.3 \text{ mm}^3$  silicon chip made in the TSMC 65nm LP RF MS CMOS process (Figure 1). It contains approximately 8 million transistors.  $SC\mu M$ -3C has 64 kB of program SRAM memory (IMEM) and 64 kB of data SRAM memory (DMEM). There are also 16 kB of program ROM which contain a bootloader. The process does not offer any writeable non-volatile storage, so every time that power is removed from the chip, both the program and data are lost.

Loading program memory can be done either optically or via a wired connection, as described in section 7. Once program memory is loaded, the chip needs to be configured for the desired functionality. SCµM-3C has a tremendous amount of configurability, most of which is not of interest to most users. For example, there are eight voltage regulators on the chip, each

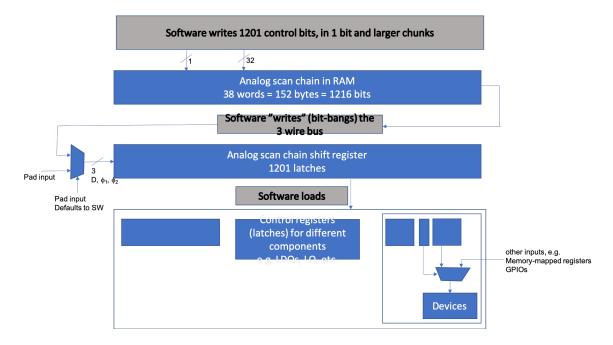

Figure 2: The Analog Scan Chain.

with a tunable output voltage. Except in rare circumstances, most of these should simply be configured to the recommended setting. Some small subset of the configurable parameters is of high importance to users, such as the radio oscillator frequency or the processor clock speed.

Configuration bits control, for example, enabling and voltage settings on LDOs, LC oscillator frequency, which oscillators are connected to which clock lines, and how the chip's pads are connected to internal inputs and outputs. Configuration bits are controlled with a combination of the Analog Scan Chain (ASC) and Memory Mapped Registers (MMR).

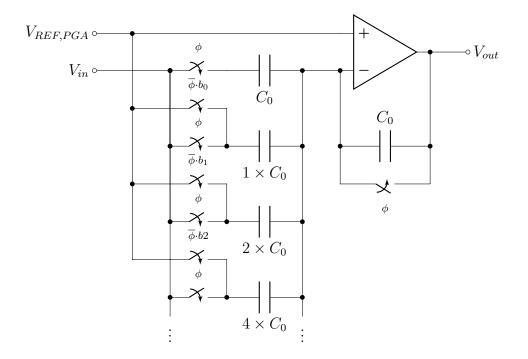

## 4.1 Analog Scan Chain

The ASC is a shift register with 1201 bits that contains almost all of the configuration information for the chip. Changing configuration with the ASC requires that the entire desired sequence of bits be shifted into position and then loaded in parallel into control registers for the various operational units on the chip (Figure 2. This process can be accomplished either from off-chip through six pads on the East side of the chip, or via software on the

Figure 3: Pad Descriptions

microprocessor. By default, the processor is in control of the ASC.

At boot, the ASC registers default to all 0. Since some of the functional units that they control need to have non-zero values during boot, this can lead to some unusual coding of control words, but most of this is hidden from the user by a collection of functions designed to simplify interface to the ASC. For example, the VDDD, AUX\_DIGITAL, and VDD\_ALWAYS\_ON voltage regulators invert the top two bits of their control word so that they are biased relatively high at boot. The ASC interface functions XXX() take this into account.

Programming the ASC requires several milliseconds, as the entire 1201 bit sequence must be shifted into the scan chain, and each bit requires several clock cycles to shift. For many operations, this is painfully slow, so a faster control mechanism is provided via memory mapped registers. Often the control authority selection between ASC and MMR is yet another ASC bit, as shown in Figure 2.

## 4.2 Memory Mapped Registers

#### 4.3 Pads

As shown in Figure 1 there are pads on three sides of the chip, known for convenience as West, South, and East. Most of the East and West pads are for debugging purposes. One notable exception is the antenna pad on the West side, labeled RF INPUT. For size-constrained applications, this can be wire bonded to any floating pad on the chip, such as ASC\_PHI1.

Supply pads with the same name are wired together on chip, and no issues have been found which would indicate that more than one bond wire is needed for VBAT (5 pads) or GND (9 pads). There are two separate pad voltage domains. VDDIO is used as the pad ESD and IO voltage domain for all of the GPIO, UART, and BOOT pads, all of which form a continuous line on the South side of the chip. All other pads use VBAT for ESD, and use a mix of VDDD and VBAT for the IO voltage. The specifics for each pad are in xxx-document.

The minimum number of pads that must be connected to boot the mote is two: VBAT and GND. For roughly half of the chips, the optical boot

| Pad Name                      | Voltage Domain | Protection | comment |

|-------------------------------|----------------|------------|---------|

| GND                           |                |            |         |

| VBAT                          |                |            |         |

| VDDIO                         |                |            |         |

| RF INPUT                      |                |            |         |

| GPIO                          | VDDIO          | VDDIO      |         |

| UART                          | VDDIO          | VDDIO      |         |

| 3WB                           | VDDIO          | VDDIO      |         |

| ADC_INPUT                     |                |            |         |

| GPO0                          |                |            |         |

| HARD_RESET                    |                |            |         |

| BOOT_SOURCE_SELECT            |                |            |         |

| Less likely to be used by app | olications     |            |         |

| VDD25                         |                |            |         |

| IF_*                          |                |            |         |

| *_LDO_OUT                     |                |            |         |

| RF_DIVIDER_OUT                |                |            |         |

| MOD CLK INPUT                 |                |            |         |

| BANDGAP OUT                   |                |            |         |

| VDD_DIVIDER                   |                |            |         |

| LF_EXT_CLK                    |                |            |         |

| ASC_*                         |                |            |         |

| VDDD_*                        |                |            |         |

Table 1: Common pads and their IO voltage and protection voltage domains.

| Domain      | leakage | powers             |

|-------------|---------|--------------------|

| VDDD        | 80      | Cortex, RAM        |

| AlwaysOn    | 45      | Optical receiver   |

| LO          | 13      |                    |

| Sensor ADC  | 12      |                    |

| Aux Digital | 8       |                    |

| IF          |         |                    |

| PA          |         | TX power amplifier |

Table 2: Voltage domains

sequence described below will work with just these two pins connected. For the other half, VDDD\_LDO\_OUT must be briefly raised to VBAT in order for the chip to boot. Exact reason and timing are under investigation.

For wired bootloading, the minimum number of pads is six: VBAT, VD-DIO, GND, and the three wire bus: BOOT\_3WB\_CLK, BOOT\_3WB\_DATA, and BOOT\_3WB\_LATCH. VDDIO may not be needed - this is still under investigation.

To make a minimal BLE or 802.15.4 transmitter sending data from the on-board temperature or lighthouse sensors, the antenna pad must also be connected. With a 3 mm wirebond across the chip, the antenna loss is approximately -25 dBi  $[\mathbf{xxx}]$ .

#### 4.4 Voltage Domains

There are eight different voltage domains and five different bandgap references feeding them.

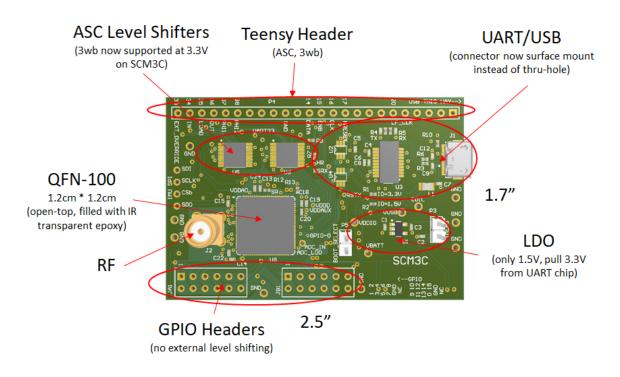

# 5 PCB Overview

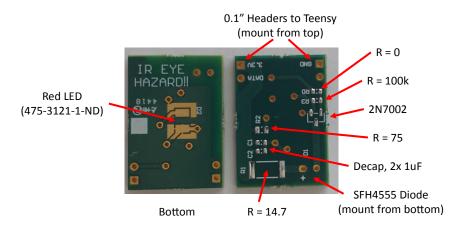

The first implementation of the 3C software development board is shown in Figure 4. The SCM chips are packaged into QFN-100 packages from Quik-Pak to make them replaceable, reduce the board cost (relaxed trace/space), and to speed up board assembly. The PCBs use ENIG surface treatment so it is possible to directly wirebond to them although the bonds and angles can get rather extreme due to the large QFN landing. The boards also include a SMA connector to ease RF testing, all GPIOs broken out on 0.1" headers, and

Figure 4: SCM-3C Software Development PCB

UART/USB conversion. The boards are powered via the 5V USB connection and a 1.5V LDO is included to generate VBAT for SCM (with an inline jumper to make it easier to measure current). The FTDI UART/USB chip generates a 3.3V supply internally which can be used for VDDIO. A zero-ohm jumper on the board determines whether VDDIO on SCM is connected to the 3.3V or 1.5V supply domain. The Teensy header and ASC level shifters are not used since the analog scan chain can be controlled from the Cortex on chip and optical bootload is easier than wired programming. A future board revision could be made smaller by removing the Teensy header and level shifters as well as moving the UART/USB bridge off board - perhaps instead to one of FTDIs cable-based solutions. The back side of the PCB also has footprints included for an Invensense IMU (should support either the MPU-9250 or newer ICM-20948), a ADT7302 SPI temperature sensor, and a LTC4123 wireless battery charger. There is also a footprint for attaching a coin cell battery holder.

# 6 Electrical Specification

# 7 Bootloading

There are two bootload modes: optical and wired. The mote defaults to optical bootload mode which requires no external connections. The "bootload\_source\_select" pin is used to switch the mote to wired mode. This pin is internally pulled to ground selecting optical mode, and should be driven high (either to VDDD or VBAT) to select wired boot mode. See Appendix B in [4] for hardware details on the on-chip optical receiver. See [3] for details on the 3-wire bus mode.

## 7.1 Optical Bootloading

#### WARNING

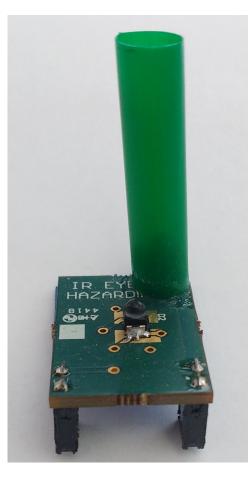

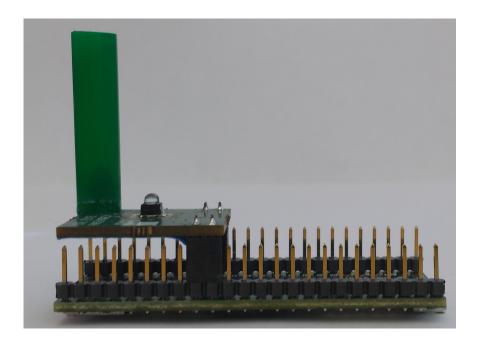

The optical programmer uses a high intensity OSRAM SFH4555 nonvisible infrared LED which outputs enough power to cause eye and skin damage at short range or prolonged exposure. As a general safety rule, always treat the programmer as if it were active, even when you know it is not. A visible red warning LED is included on the transmitter PCB to indicate when power is applied to the LED driver. It is recommended to turn off power to the transmitter Teensy when not in use.

For the approximately 1s duration of programming when the LED is active, the minimum safe distance is about 3 cm. A standoff is recommended to physically prevent getting closer than this to the LED. A section of a straw serves the purpose well and also provides a guide for aiming the LED at the chip.

Both optical and wired programming use a Teensy 3.6 for the programmer. The same Arduino firmware is used for both modes and is available on Box. When flashing the Teensy with code it is best to only have one Teensy plugged in at a time to ensure you are programming the correct device. Both MAT-LAB and Python are supported for transferring a compiled binary from Keil (the .bin file) to the Teensy which then programs the mote. The programming scripts are available on Box and should be updated with the appropriate COM port and path to the binary file. Flags set which bootload mode is used. The script also optionally allows for adding CRC checking to ensure the integrity of the software payload after it is transferred over optical into SRAM. The Keil project for SCM must include support for CRC checking (see software in git repo) as the length and CRC are written to memory locations that are predefined in the software. The bootloader script also has flags for choosing to fill unused program memory with zeros or random data. This can be useful for checking for errors during programmed or checking that SRAM is fully functional. The choice of skipping hard reset during optical program is also set via a script flag.

The optical transmitter is best used at distances < 5cm with care taken to align the IR LED to the mote due to its  $\pm 5$  degree half angle. The diode/straw of the optical programmer should be roughly aimed at the photodiode on the chip which is annotated as the small black rectangle in Figure 1. Details on the optical programmer PCB can be found in Section 23 and the PCB source files are available on Box. The presence of epoxy covering the chip wirebonds appears to slightly reduce the distance that the chip can be reliably programmed. Care should be taken to avoid damaging the epoxy above the chip or allowing the photodiode to be obstructed in any way. If difficulties are encountered when programming, try adjusting the position or vertical height of the programmer. A "helping hands" solder holder is very convenient for positioning the programmer.

The programmer will send a preamble to allow the on-chip receiver to settle, then send a start symbol, followed by dummy data to wait for hard reset to execute, and then the binary program data encoded with 4B/5B. The on-chip optical receiver will wait to recognize the start symbol and will issue a hard reset to get the chip to re-execute its ROM. The receiver will then decode the data, convert it to the same format as 3-wire bus, and load the program data into SRAM. Consult [4] for further details on the on-chip optical receiver.

The programmer provides the option of whether or not to issue a hard reset to the chip prior to bootloading. For including a hard reset, the start symbol is the sequence [169 176 167 50]. For skipping the hard reset the start symbol is [184 84 89 40]. If the reset is skipped then no dummy data is sent.

## 7.2 3-Wire Bus Bootloading

The wired mode requires three wires (data, clk, latch) and is henceforth referred to as 3wb for 3-wire bus. If the mote has already been programmed once then access to Hard Reset is also needed to re-execute the boot ROM. Alternatively, power cycling will also re-execute the ROM. To switch to 3wb mode the BOOTLOAD\_SOURCE\_SELECT pin must be pulled high to VBAT. A jumper position is provided on the PCB for this purpose. Note that pulling this pin high also disables the optical receiver analog frontend.

The same Teensy 3.6 microcontroller and firmware is used for 3wb bootloading. The clock, data, latch, and hard reset pins should be connected to their respective pins on SCM. Level-shifters are not required for clock, data, and latch on 3C whereas they were on earlier versions. The hard reset pin on SCM however will not tolerate 3.3V so either a level shifter is required or the Teensy should be configured as an open drain output for that pin (since the chip has an internal pullup). A compiled binary is loaded onto the mote using the same MATLAB or Python scripts which interface to the Teensy.

## 7.3 Mote Startup

When the mote first boots up it executes the following steps from ROM:

- Set BOOT\_MODE to 3wb

- Assert GPIO-0 high

- Wait until 64 kB have been written to IMEM via 3wb interface

- Set BOOT\_MODE to none (regular execution)

- Switch instruction execution from ROM to RAM

- Issue a soft reset

After soft reset has finished the mote should be running the software that was bootloaded into RAM. A useful troubleshooting step for debugging startup is to see if GPIO-0 is high. If it is then the mote is likely waiting to be bootloaded. If not, then something went wrong with the startup process. Other useful debug steps are to check that HCLK is coming out GPIO<sub>i</sub>12; and that both hard (GPIO<sub>i</sub>13;) and soft (GPIO<sub>i</sub>14;) resets are high. It is recommended to consult [3] for further details.

## 7.4 Optical Boot Troubleshoot

More often than not when optical programming is being problematic the issue is alignment or distance related. Moving the programmer slightly and trying a few times is generally enough to resolve the issue. If problems persist then make sure there is nothing obstructing the photo diode. Take care to not make contact with the epoxy covering the chip as it can become marred and lead to issues with light reaching the photo diode.

A more detailed debugging step involves looking at the signals coming out of the optical receiver through the GPIO bank. When the mote first boots up it defaults to GPIO bank 0 which outputs OPTICAL\_CLK\_RAW and OPTICAL\_DATA\_RAW. Observing these two signals at the same time will shed some light on whether the alignment is correct. These signals should be time shifted versions of one another and the width of the narrow pulses should be shorter than the time shift between the two traces. Another debugging step is to check whether Hard Reset is being asserted during the programming process. If Hard Reset is occurring then at least some of the bits are being properly received but perhaps not the entire 64 kB is error free. If there is no Hard Reset then either something else is wrong or the alignment is so poor that even the first 32 bits are not being properly received.

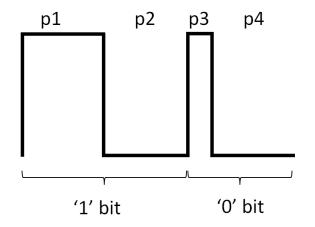

It is possible to adjust the pulse width parameters that the Teensy uses when flashing the programming LED. Figure 5 shows the parameters that are used to set the on and off times for one and zero data bits. These values are passed to the Teensy in the bootloader script using the command 'configopt' followed by four integer values. These values are used as a for loop index that ultimately determines how wide each pulse is. The values {80,80,3,80} were determined experimentally to work relatively well but are unlikely to be optimum. The third value is likely to be the most beneficial to tweak as it determines the width of the zero bit pulse, which is the most critical for achieving error free operation.

# 8 Misc Optical Bootload Related Items

## 8.1 Optical Data Transfer

The optical receiver also provides a mechanism for wirelessly sending data to the mote after it has been programmed. Bits received over optical are clocked into a 32-bit shift register and an interrupt called "optical\_irq\_in"

Figure 5: Variables describing pulse width properties of the Teensy optical transmitter.

is asserted every 32 new bits. A SFD (start frame delimiter) of [221 176 231 47] is also available to help synchronize the mote to the data sequence to be transferred. When the 32-bit register matches this value, a separate interrupt called "optical\_sfd\_interrupt" is asserted. By first waiting for the SFD interrupt and then reading the new data every time the "optical\_irq\_in" IRQ executes, one can send commands or transfer arbitrary amounts of data to the mote and have it stored in DMEM.

analog\_rdata[335:304] = Optical 32-bit Register

## 8.2 Optical Timing Transfer

Since the mote needs programmed every time it loses power, bootloading provides an opportunity to also provide initial timing calibration. That can be accomplished by sending the optical SFD sequence at a fixed rate after bootload has completed. This will cause the optical SFD interrupt to go off at a known rate which can be used to calibrate the clocks on chip. The timing interval of the interrupt is based on the crystal-based Teensy clock and is thus much more accurate than SCM.

## 8.3 Lighthouse Localization Receiver

The optical receiver on SCM can also be used at limited range to receive localization pulses from a HTC Lighthouse. A demo of this capability is included in the Git repo.

## 8.4 Future Feature Idea: Hardware IDs & Calibration Data

While SCM has no hardware support for permanently setting identifying addresses on a per-node basis, this functionality could be added to the bootloader script. In the same way that the CRC is calculated and then inserted at a known memory location in the payload, an unique identifying address could be inserted during the programming process for individual nodes. The same technique could be used for inserting calibration tables into memory if desired.

## 8.5 Future Feature Idea: RF Bootloader

While not officially implemented or even attempted, it may be possible to implement an RF reprogramming capability by executing instructions out of data memory. The FPGA version of SCM will execute from DMEM but with strange behavior. The memory instantiations are not identical between ASIC and FPGA versions so it is possible that the ASIC version behaves differently when executing from DMEM (Modelsim indicates this is the case). If the ASIC version is capable of executing from DMEM, then it may be possible to copy new binary data into DMEM from whatever source desired, ie over the air via the radio, and then transfer execution to those new instructions. Note that using DMEM is required since IMEM becomes read-only after the initial bootload process. Also note that the mote would first need programmed with software to support this functionality so its utility is limited (ie this won't let you RF bootload from cold startup).

# 9 GPIO

1 % GPIO Direction Control

2 % 1 = output, 0 = input

```

3 % out_mask<0:15> = gpio_direction;

4 % in_mask<0:15> = 1 - gpio_direction;

6 % On-chip mapping is:

7 % out_en<0:15> = ASC<1131>,ASC<1133>,ASC<1135>,ASC<1137>,

8 %

ASC<1140>, ASC<1142>, ASC<1144>, ASC<1146>,

9 %

ASC<1115>, ASC<1117>, ASC<1119>, ASC<1121>,

10 %

ASC<1124>, ASC<1126>, ASC<1128>, ASC<1130>

11

12 % in_en<0:15> = ASC<1132>,ASC<1134>,ASC<1136>,ASC<1138>,

13 %

ASC<1139>, ASC<1141>, ASC<1143>, ASC<1145>,

14 %

ASC<1116>,ASC<1118>,ASC<1120>,ASC<1122>,

15 %

ASC<1123>, ASC<1125>, ASC<1127>, ASC<1129>

16

17 ASC(1131:2:1137) = 1 - out_mask(1:4);

//Outputs are active low

18 ASC(1140:2:1146) = 1 - out_mask(5:8);

19 ASC(1115:2:1121) = 1 - out_mask(9:12);

20 ASC(1124:2:1130) = 1 - out_mask(13:16);

21

22 ASC(1132:2:1138) = in_mask(1:4);

//Inputs are active high

23 ASC(1139:2:1145) = in_mask(5:8);

24 ASC(1116:2:1122) = in_mask(9:12);

25 ASC(1123:2:1129) = in_mask(13:16);

```

| 1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <th1< th=""> <th1< th=""> <th1< th=""> <th1< th=""></th1<></th1<></th1<></th1<> | NII         NIII         NIIII         NIIII         NIIII         NIIII         NIIII         NIIII         NIIIII         NIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ê de la companya de la company                                                                                                                                                                                                                                                                                                                   |

Figure 6: GPIO Bank

# 10 Interrupts

There are four external interrupts available in the GPIO bank with various trigger polarities and debouncing. All four are synchronized to HCLK.

EXT\_INTERRUPT<0> is debounced, and is active high EXT\_INTERRUPT<1> is not debounced, and is active high EXT\_INTERRUPT<2> is not debounced, and is active low EXT\_INTERRUPT<3> is not debounced, and is active low

The interrupt mask is set using the register 0xE000E100 in the startup file (cm0dsasm.s). The order of the interrupt mask is as follows, ordered from LSB to MSB. For example, to activate only the UART and RFTIMER ISRs the mask would be 0x0081.

```

UART

interrupt_gpio3_activehigh_debounced

optical_irq_in

ADC

0

0

RF_FSM

RFTIMER

interrupt_rawchips_startval

interrupt_rawchips_32

0

optical_sfd_interrupt

interrupt_gpio8_activehigh

interrupt_gpio9_activelow

interrupt_gpio10_activelow

0

```

These are useful macros for dynamically controlling interrupts. See ARM documentation for further details.

```

// Interrupt set enable reg

#define ISER *(unsigned int*)(0xE000E100)

// Interrupt clear enable reg

#define ICER *(unsigned int*)(0xE000E180)

```

```

// Interrupt clear pending reg

#define ICPR *(unsigned int*)(0xE000E280)

// Interrupt set pending reg

#define ISPR *(unsigned int*)(0xE000E200)

```

# 11 UART

SCM has no JTAG capability so UART is the primary debugging method. All printf output is printed out over UART. Assuming a 5 MHz HCLK frequency the default baud rate is 19200. If HCLK is some other frequency then the baud rate should be adjusted accordingly since the divide ratio is fixed (e.x. if you doubled HCLK to 10 MHz you should set baud rate to 38400). Other settings that should be used: 8 data bits, 1 stop bit, and no parity. Every character input to SCM via the UART will cause an interrupt to go off. Each character needs to be read as SCM doesn't have any UART framing capability. See the demo software for how to send commands to the chip. A three character format is adopted where three ASCII characters are sent to the chip followed by a newline (e.x. sta\n). A bank of IF statements checks to see if the input command sequence matches any of the pre-programmed ones and then executes the appropriate section of code.

A link to to a useful terminal program for Windows is given below. This program is useful for passively monitoring debug output from the chip as well as sending commands over UART. It is also possible to both send and receive UART data from Python or MATLAB. This can be a very useful way to automate data collection and testing.

https://sites.google.com/site/terminalbpp/

# 12 SPI

# 13 Clock Configuration

# 14 Frequency Counters

# 15 Timers

See Section 3.35 in [3] for a detailed description of the RFTIMER module. Note the design assumption that HCLK and RFTIMER are phase aligned. This means that both clocks should be derived from the same oscillator and that HCLK must be an integer multiple of RFTIMER. A moderately complex example of using the RFTIMER module can be found in the 802.15.4 TSCH demo in the Git repo. Unfortunately only 8-bit frequency dividers are available for generating the RFTIMER clock (The JIRA feature SCUM-124 for changing to a 16-bit divider was not able to be added to SCM-3C in time for tape-out).

# 16 LO, PA, and Divider Hardware Details

## 16.1 Analog Scan Chain

In this section I will attempt to describe the functionality of the chain bits. The scan chain is nominally controlled by functions from the Cortex M0, so I will not go into excessive detail regarding the exact bits in the array that need to be changed to perform certain functions. Rather, I will describe them in chunks.

- fine\_code 5 bit control of the LC tank's fine tuning DAC f0, ... ,f4, fd

- mid\_code 5 bit control of the LC tank's mid tuning DAC m0, ... m4, md

- coarse\_code 5 bit control of the LC tank's coarse tuning DAC c0, ... c4, cd

- lo\_tune\_select set to 0 for LC control from the Cortex analog\_cfg, 1 for scan

- polyphase\_enable set to 0 to disable the polyphase filter. 1 to enable.

- lo\_current\_tune 8 bit control of LC tank's current between 180  $\mu$ A and 800 $\mu$ A LSB to MSB.

- test\_bg 7 bit control of the test band gap (connected to pad) from 0.75 V to 0.85 V if MSB = 0, and from 1.05 V to 1.12 V if MSB = 1 (panic).

- pa\_ldo\_rdac see test\_bg, controls power amplifier supply.

- lo\_ldo\_rdac see test\_bg, controls LO supply.

- div\_ldo\_rdac see test\_bg, controls divider supply.

- mod\_logic controls the source of modulation for the 802.15.4 capacitor. The MSB determines whether the modulation is inverted or not (1 for inversion). The next bit selects cortex or pad modulation (0 for cortex, 1 for pad). The next two bits can be used to test the modulation, setting the control bit to VDD or to ground. Note: for 802.15.4 modulation,

the bits should be set to 1000. For BLE modulation from pad using the 802.15.4 capacitor, it should be set to 0111. A schematic of this control is shown in Fig. 7.

- mod\_15\_4\_tune tunes the frequency spacing of the 802.15.4 modulation capacitor. 4 bits, but the LSB is a dummy (not binary weighted).

- sel\_1mhz\_2mhz 0 uses the x2 XOR multiplier. 1 is pass through.

- pre\_2\_backup\_en enables the static flip flop div-by-2 prescaler.

- pre\_5\_backup\_en enables the static flip flop div-by-5 prescaler. This is recommended for standard operation.

- pre\_dyn is a 3-bit, one-hot selection of three different injection-lock TSPC-esque pre-scalers. It needs to be inverted (so all 1s will disable all three dynamic pre-scalers). The second of the three is the strongest, and will result in a div-by-2 for almost all LO and divider settings. The first can consistently give a div-by-5 for most settings. The third one is the weakest, and it is possible to divide by up to 7 using it.

- div\_64mhz\_enable enables a 64 MHz output frequency divider to clock the baseband stages and receiver ADC.

- div\_20mhz\_enable enables a 20 MHz output frequency divider to clock the BLE GFSK module. This is also the clock output that is connected to the LC counter.

- div\_static\_code sets the static divider ratio. This can also be controlled from the Cortex's analog\_config, and generally should be. More on that later.

- div\_static\_reset\_b active low reset of the static divider.

- dyn\_div\_N there is another, theoretically lower power, divider on the chip as well. It has never been tested.

- div\_tune\_select set to 0 to have the divider controlled from the cortex. Set to 1 for the divider to be controlled from scan chain.

- BLE\_module\_settings will be obfuscated in future versions of the chip.

Figure 7: 802.15.4 Modulation Logic Schematic

## 16.2 Cortex Code

I will now describe some of the very low-level functions for directly controlling parts of the transmitter from the cortex. Start with the relevant config and rdata registers:

```

#define ACFG_DIV_ADDR *(unsigned int*)(APB_ANALOG_CFG_BASE + 0x00140000)

#define ACFG_DIV_ADDR_2 *(unsigned int*)(APB_ANALOG_CFG_BASE + 0x00180000)

#define ACFG_LO_ADDR *(unsigned int*)(APB_ANALOG_CFG_BASE + 0x001C0000)

#define ACFG_LO_ADDR_2 *(unsigned int*)(APB_ANALOG_CFG_BASE + 0x00200000)

```

#define ASYNC\_FIFO\_\_ADDR \*(unsigned int\*)(APB\_ANALOG\_CFG\_BASE + 0x00680000)

ACFG\_DIV\_\_ADDR contains two control bits to set the RF divider divide ratio.

ACFG\_DIV\_\_ADDR\_2 has the remaining control bits, as well as enable and reset signals for the divider. Quick note here: this divider struggles at low supply voltages, and will not work for odd divide ratios if the input frequency is high (around 1.2 GHz). The code to control these divider registers is called digProgram(div\_ratio, reset, enable). Reset is active low. A diagram of these two registers is shown in Fig. 8. The pre-scaler must be enabled for this divider to have an output (see scan chain for details).

../figures/appendix/div\_reg\_small.pdf

Figure 8: Divider registers, bit by bit

ACFG\_LO\_\_ADDR\_2 has the fine frequency control LSB and fine frequency

control dummy bit. ACFG\_LO\_\_ADDR has the remaining control bits. The function LC\_FREQCHANGE(coarse, mid, fine) controls these overlapping capacitor DACs. This function obfuscates the dummy bits. The function LC\_monotonic(LC\_code, mid\_divs, coarse\_divs) implements the function in Chapter 6. If you are tuning the LC oscillator, this you will probably use LC\_monotonic. In any case, the diagram of the two LC control registers is shown in Fig. 9. The bits labeled with a "d" are the dummy bits, and will change the frequency by approximately five LSBs of the given DAC.

../figures/appendix/lo\_reg\_small.pdf

Figure 9: Oscillator frequency tune registers, bit by bit

There are a number of functions that control the scan chain, but they are relatively straightforward, especially considering the exposition given in the previous section. There are also a functions written to generate BLE advertising packets (gen\_ble\_packet) and to use the on-chip asynchronous FIFO to transmit BLE packets (transmit\_ble\_packet). At the moment, they are designed for transmitting 128 bit packets but they can easily be repurposed to transmit larger payloads. The transmit function in particular can be repurposed with completely arbitrary data for potential experimentation with 802.15.4 chipping sequences.

## 16.3 Common Configurations

This section describes the necessary scan/Cortex procedure to use the radio in various modes.

#### 16.3.1 Receive Mode (RF only)

- 1. Enable the LC tank LDO and current source. This can be done either through GPIO (for fast start) or with the scan chain. Enabling the LC tank can be configured to start automatically via the radio state machine on SCM v3b.

- 2. Set the LC tank current to an appropriate level (most people have used a current level of 127 - this appears to offer a good tradeoff between

PA efficiency, LO current, and phase noise).

- 3. Enable the polyphase filter.

- 4. Program the LC tank so that it is 2.5 MHz ABOVE the receive channel frequency.

- 5. Enable the IF chain and digital baseband. This is documented elsewhere.

#### 16.3.2 Transmit Mode - 802.15.4

- 1. Enable the LC tank LDO and current source.

- 2. Enable the PA LDO. Again, on SCM v3 this can be done with either GPIO (fast) or scan chain.

- 3. Ensure that the polyphase filter is disabled.

- 4. Tune the LC tank frequency to 500 kHz ABOVE the desired channel frequency.

- 5. If data is transmitted from the on-chip state machine, set the four mod\_logic bits to 1000. If data is transmitted from a pad, set mod\_logic to 1000. The bit-bang direct modulation is inverted from the bits coming from the state machine.

- 6. Ensure that the transmit clock (source can be chosen) is within 40 ppm of 2 MHz.

- 7. Use instructions in [Sahar'thesis] to load and transmit a packet.

#### 16.3.3 Transmit Mode - BLE

- 1. Enable the LC tank LDO and current source.

- 2. Enable the PA LDO.

- 3. Enable the divider LDO. The divider does not need to run, BUT the data buffers run off of the divider supply.

- 4. Ensure that the polyphase filter is disabled.

- 5. Tune the LC tank frequency to approximately 250 kHz BELOW the desired channel frequency.

- 6. Disable the 802.15.4 DAC by setting mod\_logic to 0010 or 0001.

- 7. If data is transmitted from a pad, set the mod\_logic bits to 0010. If data is transmitted from the Cortex (requires some trickery here: the Cortex clock needs to be an exact integer multiple of 1 MHz, and bits go straight from memory mapped IO to the LC tank. This also requires assembly code. Fortunately Keil allows in-line assembly).

- 8. Bypass both the FIFO and the GFSK module.

- 9. Run the BLE transmitting assembly code.

It is also possible to use the 802.15.4 capacitor DAC to transmit BLE. However, this is only possible from off-chip. The only DAC that can be controlled directly from the Cortex is the set of 500 kHz BLE capacitors. On SCM v3b, this procedure will be significantly different for two reasons. First, there is a 2048-bit FIFO so that the Cortex does not need to run at an exact multiple of 1 MHz. Second, there is a multiplexer to select whether the data goes to the 802.15.4 capacitors or the BLE capacitors.

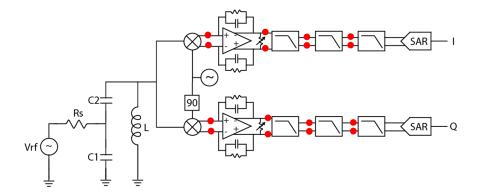

# 17 RF Receiver Analog Scan Chain

The portion of the analog scan chain (ASC) that connects to the receiver analog circuits (some of the ASC also connects to digital baseband) are largely unchanged between all hardware generations. The exception being the clock generation which has an addition bit called 'high\_range' which extends the upper frequency range of the oscillator. All of these settings are already initialized to appropriate values in software but this section is included to document the control settings.

## 17.1 Mixer Bias

Mixer DC bias is set by driving a programmable current source through a variably sized diode connected load. The LO is then AC coupled to the mixer gates. There are four total mixer switches, a differential set each for I and Q labeled as Ip, In, Qp, and Qn.

The diode connected load is labeled as ndac and consists of four equally sized devices connected in parallel. The four bit scan code is thermometer and each bit turns on an individual diode connected nmos. Setting all bits to '1' generates the lowest bias voltage.

```

ASC<294:297> = mix_bias_In_ndac<4:1>

ASC<299:302> = mix_bias_Ip_ndac<4:1>

ASC<303:306> = mix_bias_Qn_ndac<4:1>

ASC<308:311> = mix_bias_Qp_ndac<4:1>

```

The current sources are labeled as pdac and consist of 16 equally sized current sources in parallel. The four bit pdac code is binary weighted and a '0' activates the current source. ie all zeros is the most current and thus the highest bias voltage.

```

ASC<312:315> = mix_bias_In_pdac<4:1> (<4(MSB):1>)

ASC<316:319> = mix_bias_Ip_pdac<4:1>

ASC<320:323> = mix_bias_Qn_pdac<4:1>

ASC<324:327> = mix_bias_Qp_pdac<4:1>

```

The I/Q mixers can be independently disabled by these two bits. When disabled the mixer DNW goes high impedance in an attempt to improve PA efficiency so the mixers should be disabled when transmitting. '0' is enabled and '1' is disabled. Note that 3C added a memory map control option for enabling and disabling the mixers which is discussed in Section 18.3.

```

ASC<298> = mix_off_i

ASC<307> = mix_off_q

```

## **17.2** Transimpedance Amplifiers

Each transimpedance amplifier has enable, bandwidth, and gain control bits. Each TIA has three separate enable bits to allow for flexibility in shutdown modes. The amplifiers are inverter-based and have separate enable bits for the nmos and pmos labeled as 'enn' and 'enp' respectively. There is another control bit which activates a pull-down switch to ground the TIA inputs. This pulls the bottom plate of the AC coupling caps to ground and makes the mixer essentially operate in voltage mode driving a capacitive load. Bandwidth control is binary weighted with all '1's setting the bandwidth to its minimum value.

```

ASC<328:331> = tia_cap_on<4:1> (<4(MSB):1>)

ASC<332> = tia_pulldown (1=pull TIA input to ground)

ASC<333> = tia_enn (1=enabled)

ASC<334> = tia_enp (0=enabled)

ASC<462> = tia_enp (0=enabled)

ASC<463> = tia_enn (1=enabled)

ASC<464> = tia_pulldown (1=pull TIA input to ground)

ASC<465:468> = tia_cap_on<1:4> (<1:4(MSB)>)

```

## 17.3 Gain Control

```

Determines whether gain is controlled by scan chain or AGC:

'1' = AGC control, '0' = ASC

ASC<271> = agc_gain_mode (Q chan)

ASC<491> = agc_gain_mode (I chan)

```

Gain control code, d63 is max gain: As value is decreased from d63, first the TIA gain is decreased, followed by stage 1 gm, then stage 2 gm.

```

ASC<272:277> = code_scan<5:0> Q chan (<5(MSB):0>)

ASC<485:490> = code_scan<0:5> I chan (<0:5(MSB)>)

Gm control for filter stage 3 (ADC driver); thermometer coded.

All '1's = max gm.

ASC<278:290> = stg3_gm_tune<1:13>

ASC<472:484> = stg3_gm_tune<13:1>

```

#### 17.4 Filters

Each filter stage has control over the amplifier enable, the clock enable, and tuning of the capacitor ratio that sets the filter's pole location. The transconductance of each stage is controlled as described in the gain control section.

```

Q Chan amplifier enables:

ASC<347> = stg3_amp_en

ASC<351> = stg2_amp_en

ASC<355> = stg1_amp_en

Q Chan individual clock enables:

ASC<369> = stg3_clk_en

ASC<376> = stg2_clk_en

ASC<383> = stg1_clk_en

Q Chan stage 3 cap ratio:

ASC<370:372> = stg3_C2<3:1>

ASC<373:375> = stg3_C1<3:1>

Q Chan stage 2 cap ratio:

ASC<377:379> = stg2_C2<3:1>

ASC<380:382> = stg2_C1<3:1>

Q Chan stage 1 cap ratio:

ASC<384:386> = stg1_C2<3:1>

ASC<387:389> = stg1_C1<3:1>

I Chan amplifier enables:

```

```

ASC<441> = stg1_amp_en

ASC<445> = stg2_amp_en

ASC<449> = stg3_amp_en

I Chan individual clock enables:

ASC<400> = stg3_clk_en

ASC<407> = stg2_clk_en

ASC<414> = stg1_clk_en

I Chan stage 3 cap ratio:

ASC<401:403> = stg3_C2<3:1>

ASC<404:406> = stg3_C1<3:1>

I Chan stage 2 cap ratio:

ASC<408:410> = stg2_C2<3:1>

ASC<411:413> = stg2_C1<3:1>

I Chan stage 1 cap ratio:

ASC<415:417> = stg1_C2<3:1>

ASC<418:420> = stg1_C1<3:1>

```

## 17.5 ADC

```

Q Chan comparator offset trim:

Binary weighted, increase from 0 to add cap to either side of comparator.

ASC<335:339> = pctrcl<4:0> (<4(MSB):0>)

ASC<340:344> = nctrcl<4:0>

Activate 1-bit mode for ZCC on Q channel:

ASC<345> = mode_1bit

Enable Q channel comparator:

ASC<346> = adc_comp_en

Enable Q channel ADC FSM:

ASC<367> = adc_fsm_en

```

```

Q channel common mode reference generation:

Separate amp/clock enables;

The select signal controls a capacitive voltage divider.

ASC<359> = vcm_amp_en

ASC<360:361> = vcm_vdiv_sel<0:1>

ASC<362> = vcm_clk_en

```

```

Q channel reference voltage generation:

Separate amp/clock enables;

The select signal controls a capacitive voltage divider.

ASC<363> = vref_clk_en

ASC<364:365> = vref_vdiv_sel<1:0>

ASC<366> = vref_amp_en

```

```

I channel common mode reference generation:

Separate amp/clock enables;

The select signal controls a capacitive voltage divider.

ASC<390> = vcm_amp_en

ASC<391:392> = vcm_vdiv_sel<0:1>

ASC<393> = vcm_clk_en

```

```

I channel reference voltage generation:

Separate amp/clock enables;

The select signal controls a capacitive voltage divider.

ASC<394> = vref_clk_en

ASC<395:396> = vref_vdiv_sel<1:0>

ASC<397> = vref_amp_en

```

```

Enable I channel ADC FSM:

ASC<398> = adc_fsm_en

```

```

Enable I channel comparator:

ASC<450> = adc_comp_en

```

```

Activate 1-bit mode for ZCC on I channel:

```

$ASC<451> = mode_1bit$

```

I Chan comparator offset trim:

Binary weighted, increase from 0 to add cap to either side of comparator.

ASC<452:456> = nctrl<0:4> (<0:4(MSB)>)

ASC<457:461> = pctrl<0:4>

```

## 17.6 Clock Generation

```

Enables for filter and ADC clock generation; '1' = on

ASC<422> = adc_phi_en

ASC<423> = filt_phi_en

Mux select for IF clock source:

00=gnd, 01=internal RC, 10=divided LC, 11=external pad

```

```

ASC<424:425> = clk_select<1:0>

```

IF RC clock enable; '1' = on

ASC<426> = RC\_clk\_en

```

Coarse and fine frequency tune, binary weighted

ASC<427:431> = RC_coarse<4:0> (<4(MSB):0>)

ASC<433:437> = RC_fine<4:0> (<4(MSB):0>)

```

```

Switch between high and low speed ranges for IF RC:

'1' = high range

ASC<726> = RC_high_speed_mode

```

#### 17.7 LDO and Reset

```

Resistor for setting bandgap reference voltage

ASC<492:498> = if_ldo_rdac<0:6> (<0:6(MSB)>)

'1' = disable ability for POR to reset IF blocks

ASC<499> = por_disable

```

Figure 10: IF Debugging Path

'0' = force reset from scan chain ASC<500> = scan\_reset

## 17.8 Debug Path

IF debugging access is available at the nodes marked with dots in Figure 10. Differential IF signals are connected to source followers to pseudodifferentially route signals out to an off-chip instrumentation amplifier for viewing. The four possible observation locations all share a pair of chip pads and thus should only be turned on one at a time. Input stimulus can also be injected at these same locations from off-chip. A differential pair of input pads is driven from an off-chip single ended to differential converter. The I and Q paths have independent debug paths and thus there are 8 total pads used for debug observation (2 inputs and 2 outputs for I, 2 inputs and 2 outputs for Q).

The debug path is controlled by an enable bit to activate the source follower bias, a bit to enable an analog pass gate connecting the source follower output to the pads, and a bit which enables another analog pass gate connecting the input pads to a particular node. Thus each of the 8 total debug access points are controlled by 3 bits each for a total of 24 scan bits.

Q channel mixer output node: ASC<291> = dbg\_bias\_en\_Q ASC<292> = dbg\_out\_en\_Q ASC<293> = dbg\_input\_en\_Q

```

Q channel input to stage 3 filter:

ASC<348> = dbg_out_on_stg3

ASC<349> = dbg_input_on_stg3

ASC<350> = dbg_bias_en_stg3

Q channel input to stage 2 filter:

ASC<352> = dbg_out_on_stg2

ASC<353> = dbg_input_on_stg2

ASC<354> = dbg_bias_en_stg2

Q channel input to stage 1 filter:

ASC<356> = dbg_out_on_stg1

ASC<357> = dbg_input_on_stg1

ASC<358> = dbg_bias_en_stg1

I channel input to stage 1 filter:

ASC<438> = dbg_bias_en_stg1

ASC<439> = dbg_input_on_stg1

ASC<440> = dbg_out_on_stg1

I channel input to stage 2 filter:

ASC<442> = dbg_bias_en_stg2

ASC<443> = dbg_input_on_stg2

ASC<444> = dbg_out_on_stg2

I channel input to stage 3 filter:

ASC<469> = dbg_input_on_I

ASC<470> = dbg_out_on_I

ASC<471> = dbg_bias_en_I

I channel input to stage 3 filter:

ASC<446> = dbg_bias_en_stg3

ASC<447> = dbg_input_on_stg3

ASC<448> = dbg_out_on_stg3

```

There are also digital output signals which can be enabled for the ADCs and clock generation. The ADC debug outputs allow observation of internal ADC FSM signals. The clock debug signals enable the output of the multiphase clock signals used to run the filters and ADC. All signals are output through GPIO.

ASC<368> = Enable I channel ADC debug outputs

ASC<399> = Enable Q channel ADC debug outputs

ASC<421> = Enable debug output of ADC clock phases

ASC<432> = Enable debug output of filter clock phases

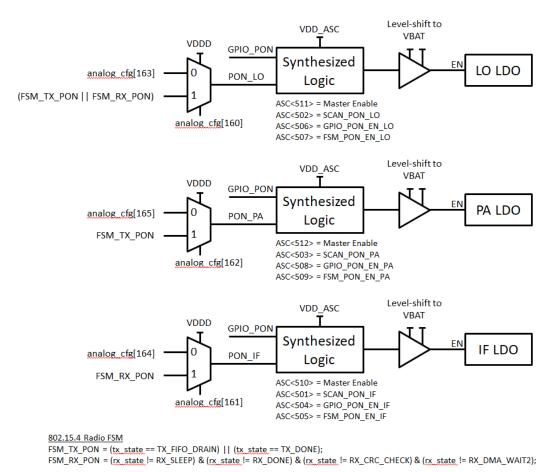

# 18 Power On Control

Several LDO control methods are implemented to enable flexibility in quickly turning the transceiver on and off for tightly duty cycled operation. There are four separate LDOs in the transceiver: the LO, PA, divider, and IF. Each can be independently controlled through any combination of the means outlined below. The possible ways to turn on an LDO are: scan chain, GP input, hardware FSM control, and through memory mapped registers from the Cortex-M0. Note that there is a fairly significant difference in the implementation of this power control logic between SCM3 and SCM3B/C. The memory mapped control option is only available in 3C.

At the time of this writing, the most practical control method appears to be using the memory mapped control option. While this does require the Cortex-M0 to be involved, it only needs to respond to an interrupt long enough to toggle one memory mapped register and then exit. This is primarily due to the turn-on time requirements of the LO. At the time when the radio FSM was designed, no consideration had been given to how long it would take for LO start-up to occur, so there is no handling of that in the FSM. Thus the FSM based control signals only assert at the actual packet event times, not offset by a start-up period.

The four ASC control signals for each LDO:

```

master_ldo_en = '0' will force the LDO off, regardless of other settings

scan_pon = '1' turns on the LDO via scan chain

gpio_pon_en = '1' allows the LDO to be turned on via GPIO_PON input

fsm_pon_en = '1' allows the LDO to be turned on via PON_XX signal

```

Verilog implementation of the power on logic:

```

assign x1 = gpio_pon && gpio_pon_en_xx;

assign x2 = fsm_pon && fsm_pon_en_xx;

assign x3 = x1 || x2 || scan_pon_xx;

assign LDO_enable_xx = x3 && master_ldo_en_xx;

```

Power-on signals generated by radio FSM:

```

assign FSM_TX_PON = (tx_state == TX_FIF0_DRAIN) || (tx_state == TX_DONE);

assign FSM_RX_PON = (rx_state != RX_SLEEP) & (rx_state != RX_DONE) & ...

(rx_state != RX_CRC_CHECK) & ...

(rx_state != RX_DMA_WAIT2);

```

Individual LDO 'PON\_XX' enable signals from digital. These can be generated either directly from the radio FSM, or from memory mapped registers. The mux control signals are also set via memory mapped registers.

```

assign PON_LO = pon_cfg[0] ? (FSM_TX_PON || FSM_RX_PON) : pon_cfg[3];

assign PON_IF = pon_cfg[1] ? FSM_RX_PON : pon_cfg[4];

assign PON_PA = pon_cfg[2] ? FSM_TX_PON : pon_cfg[5];

assign PON_DIV = pon_cfg[6];

```

Memory mapped control signals for LDOs. The mux selects determine whether the hardware FSMs or a memory mapped register get connected to the LDO 'PON\_XX' signals that go to analog. For the mux selects, '1' = FSM control, '0' = memory mapped control. The memory mapped address for this register is ANALOG\_CFG\_REG\_10.

```

analog_cfg[160] = pon_cfg[0] = L0 LD0 mux select

analog_cfg[161] = pon_cfg[1] = IF LD0 mux select

analog_cfg[162] = pon_cfg[2] = PA LD0 mux select

analog_cfg[163] = pon_cfg[3] = L0 LD0 memory-mapped enable

analog_cfg[164] = pon_cfg[4] = IF LD0 memory-mapped enable

analog_cfg[165] = pon_cfg[5] = PA LD0 memory-mapped enable

analog_cfg[166] = pon_cfg[6] = Divider LD0 memory-mapped enable

analog_cfg[167] = Aux LD0 memory-mapped enable

```

The analog scan chain bits used to configure the power control block:

```

ASC<501> = scan_pon_if

ASC<502> = scan_pon_lo

ASC<503> = scan_pon_pa

```

```

ASC<504> = gpio_pon_en_if

ASC<505> = fsm_pon_en_if

ASC<506> = gpio_pon_en_lo

ASC<507> = fsm_pon_en_lo

ASC<508> = gpio_pon_en_pa

ASC<509> = fsm_pon_en_pa

ASC<510> = master_ldo_en_if

ASC<511> = master_ldo_en_lo

ASC<512> = master_ldo_en_pa

ASC<513> = scan_pon_div

ASC<514> = gpio_pon_en_div

ASC<515> = fsm_pon_en_div

ASC<516> = master_ldo_en_div

```

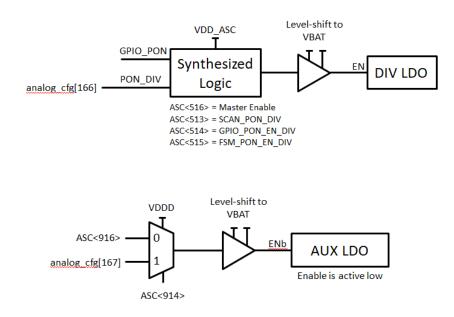

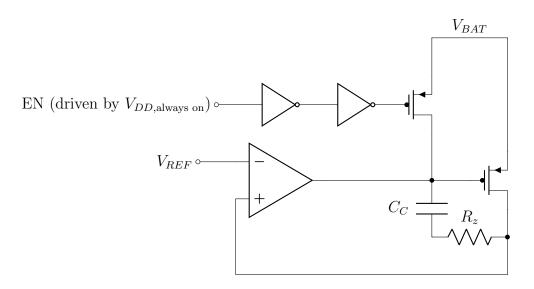

### 18.1 Aux Digital LDO

The aux digital LDO can also be turned in multiple ways. The LDO enable is multiplexed between analog scan chain and a memory mapped register as shown below. Note that per JIRA-101 an inversion was added here so that the aux digital LDO defaults to enabled at cold start. Thus the enable for the AUX LDO is active low.

#### 18.2 Power Sequencing

The LO takes >  $50\mu s$  for its frequency to settle. Turning on the PA also causes a frequency transient, but of much smaller magnitude. Ideally in transmit the LO should be turned on at least 50  $\mu s$  before the PA is activated

Figure 11: Diagram of power control options for radio LDOs.

ANALOG\_CFG\_REG\_\_10 = AUX\_EN | DIV\_EN | PA\_EN | IF\_EN | LO\_EN | PA\_MUX | IF\_MUX | LO\_MUX

Figure 12: Diagram of power control options for divider and VDD\_AUX LDOs.

to avoid broadcasting the LO settling characteristics. The PA also settles within about 50  $\mu s$ . In receive, the LO should be given enough time to settle before the start of the guard time. The IF/RX LDO can be enabled at the same time as the LO. The AUX LDO must also be enabled during both transmit and receive mode.

#### 18.3 TX/RX Switching

In addition to needing to turn the various LDOs on and off to switch between transmit and receive, the polyphase filter and mixer also need to be disabled/enabled. These can be controlled either via analog scan chain or memory mapped registers. It is recommended to use the memory mapped option to avoid the slow program time of the scan chain for fast TX/RX switching. Note that the memory mapped option is a new addition for SCM-3C. There are three bits which control whether the polyphase filter is activated and whether the mixers are switched to high impedance mode to improve the TX efficiency (there is one bit each for I and Q mixer). The memory mapped address for the analog\_cfg bits is 0x52400000 (which should have the macro name ANALOG\_CFG\_REG\_16). To use the memory mapped interface, first set all mux select bits (ASC< 744 : 746 >) to '1'.

```

Enable polyphase (In RX set to '1', in TX set to '0'):

Mux select: ASC<746>

S0: ASC<971>

S1: analog_cfg<256>

Enable I mixer (In RX set to '0', in TX set to '1'):

Mux select: ASC<744>

S0: ASC<298>

S1: analog_cfg<258>

Enable Q mixer (In RX set to '0', in TX set to '1'):

Mux select: ASC<745>

S0: ASC<307>

S1: analog_cfg<257>

To activate RX mode:

ANALOG_CFG_REG__16 = 0x1;

```

```

To activate TX mode:

ANALOG_CFG_REG__16 = 0x6;

```

## 19 Digital Baseband

Various debugging signals are available for output via the GPIO bank. Reset can come from either analog scan chain or a memory mapped register and is active low.

```

ASC<240> = mux select for reset source; 0 = ASC[241], 1 = analog_cfg[75]

ASC<241> = active low reset from ASC

Choose whether I/Q input signals are from on-chip or off-chip.

0' = On-chip

'1' = Inject from GPIO bank

ASC < 96 > = IQ\_select

Choose where IF amplifier gain control is connected

00=AGC FSM, 10 or 01=analog_cfg, 11=GPIN

ASC<102:101> = vga_gain_select

Gain control settings from memory mapped register (analog_cfg)

I channel gain = analog_cfg_agc[229:224]

Q channel gain = analog_cfg_agc[235:230]

Choice of detector for AGC

'0' = Use envelope detector, '1' = Use original overflow detector

ASC<100> = sel_envelope_0

For adding a gain offset to correct for I/Q amplitude mismatch

gain_offset = analog_cfg_agc[238:236]

Choose which channel to add gain offset to

'0' = subtract 'gain_offset' from Q channel

'1' = subtract 'gain_offset' from I channel

```

```

gain_imbalance_select = analog_cfg_agc[239]

Memory mapped register that controls how long AGC FSM waits for settling

AGC_wait_time = analog_cfg_agc[251:240]

Signal envelope level that triggers a gain reduction

Envelope_threshold = analog_cfg_agc[255:252]

Activate AGC mode where only the TIA is under automatic control

ASC < 97 > = agc_TIA_mode

Register to read the min/max values of I and Q

IQ_minmax_rdata = analog_rdata[239:224]

CDR: Sampling point for clock recovery; use 3

sample_point = analog_cfg[78:76]

CDR: Feedback parameters for clock recovery

e_k_shift = analog_cfg[58:55] Use x

tau_shift = analog_cfg[63:59]

Use x

Sign control bit for matched filter

'0' = , '1' =

ASC<103> = mf_data_sign

Memory mapped register for reading average frequency value

freq_result = analog_rdata[265:256]

freq_valid = analog_rdata[266]

// Check valid flag

if (ANALOG_CFG_REG__16 & 0x400)

return ANALOG_CFG_REG__16 & 0x3FF;

else

return 0;

```

#### 19.1 RSSI

An estimate of received signal quality can be obtained by reading the Link Quality Indicator (LQI) and RSSI registers. The RSSI value corresponds to the gain setting after Automatic Gain Control has settled and has a maximum value of 63, which roughly corresponds to an input power of  $\leq$  -85 dBm. For every unit value below 63, the received signal amplitude has increased by approximately 1 dB.

```

RSSI = analog_rdata[255:240] = (ANALOG_CFG_REG__15 & 0xOF)

```

### 19.2 Link Quality Indicator

The LQI register contains the total number of chip errors found within the first eight payload symbols. Dividing the LQI register value by 256 (8\*32) gives the corresponding chip error rate. Note that if they are less than eight payload symbols, then the error rate should be calculated by dividing by the appropriate number of total chips.

LQI = analog\_rdata[343:336] = (ANALOG\_CFG\_REG\_\_21 & OxFF)

### **19.3** Chip Rate Error Estimate

During zero-drift operation the clock and data recovery module shifts in eight new samples and outputs a strobe to the demodulator to make a decision. To correct for chip rate error it periodically clocks in either more or less than eight samples before a decision gets made. By keeping track of how many extra samples are added or dropped over the course of the packet, an estimate of the difference between the TX and RX chip rates can be obtained.

A tau value of zero indicates there is no rate mismatch between the TX and RX chip clocks. The cdr\_tau\_value corresponds to the number of samples that were added or dropped by the CDR (each sample point is 1/16MHz = 62.5 ns). For a fixed chip rate error, this value will vary depending on the length of the packet so need to convert this to a ppm error for making decisions. The RX chip clock has adjustment steps of about 2000 ppm so corrections should be made when this error exceeds about 1000 ppm. Note that the CDR tau value is a signed number. The ppm error can be calculated and then further simplified as shown below.

$$\operatorname{error\_ppm} = \frac{10^{\circ} \times (\operatorname{cdr\_tau\_value}) \times 62.5 \operatorname{ns}}{(\operatorname{packet\_length\_bytes}) \times 64 \frac{\operatorname{chips}}{\operatorname{byte}} \times 500 \frac{\operatorname{ns}}{\operatorname{chip}}}$$

(1)

$$\operatorname{cdr\_tau\_value} = \operatorname{analog\_rdata}[415:400] = \operatorname{ANALOG\_CFG\_REG\_25}$$

chip\_rate\_error\_ppm = (cdr\_tau\_value \* 15625) / (packet\_len \* 8);

# 20 Sensor ADC

#### 20.1 Hardware

This subsystem has several mutually exclusive purposes which can be chosen by modifying analog scan chain settings:

- Interface to an external sensor whose output is an analog voltage

- Battery voltage monitor

- Temperature sensor

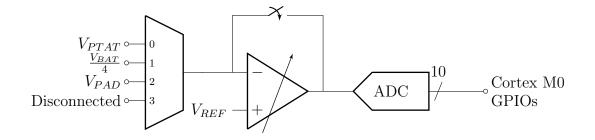

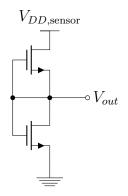

Figure 13: A pared-down block diagram of the subsystem. The key components are (1) the mux which passes the appropriate input to the sensor system (2) the programmable gain amplifier (PGA)—bypassable—which can be used to amplify the analog signal by a user-defined amount (3) the analogto-digital converter (ADC) which digitizes the analog input and can pass that information to the on-chip microprocessor or user-facing GPIOs.

Relevant code has been provided at https://github.com/PisterLab/ scum-test-code/tree/master/scm\_v3c/sensor\_adc. Information on use can be found in subsequent subsections.

| Name               | # Bits | Relevant Subsystem Scan Configuration Bits Description                            |

|--------------------|--------|-----------------------------------------------------------------------------------|

| sel_reset          | # Bits | Chooses the source for the ADC reset signal. 0 sources from                       |

| sel_reset          | L      | the taped-out FSM in digital, and 1 sources from the GPI fo                       |

|                    |        | 'adc_reset_gpi' (Figure 6).                                                       |

| sel_convert        | 1      | Chooses the source for the the-ADC-needs-to-convert signal.                       |

|                    |        | sources from the taped-out FSM in digital, and 1 sources from th                  |

|                    |        | GPI for 'adc_convert_gpi'.                                                        |

| sel_pga_amplify    | 1      | Chooses the source for the signal which tells the PGA to amplify.                 |

|                    |        | sources from the taped-out FSM in digiatl, and 1 sources from th                  |

|                    |        | GPI for 'adc_pga_amplify_gpi'.                                                    |