# Low Power, Crystal-Free Design for Monolithic Receivers

Bradley Wheeler

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2019-36 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2019/EECS-2019-36.html

May 14, 2019

Copyright © 2019, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Low Power, Crystal-Free Design for Monolithic Receivers

by

#### Bradley Wheeler

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Kristofer S. J. Pister, Chair Professor Ali M. Niknejad Professor Steven D. Glaser

Spring 2019

# Low Power, Crystal-Free Design for Monolithic Receivers

$\begin{array}{c} \text{Copyright 2019} \\ \text{by} \\ \text{Bradley Wheeler} \end{array}$

#### Abstract

Low Power, Crystal-Free Design for Monolithic Receivers

by

Bradley Wheeler

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley

Professor Kristofer S. J. Pister, Chair

Predictions of the proliferation of hundreds of billions of connected wireless devices have yet to come true. The economics of such deployments becoming feasible require that current wireless modules become smaller, cheaper, and use less power. A typical wireless device combines a RF System-on-Chip with multiple frequency references, passive components, an antenna, and a battery on a printed circuit board. The Single Chip Mote project aims to reduce the size, weight, power, and cost of these devices by eliminating the off-chip frequency references and passives. The ultimate goal being to form a 2.4 GHz wireless node by attaching only an antenna and energy source to a single CMOS die. Of particular interest is the range of applications this could enable where the size and weight of current wireless devices has prohibited their use.

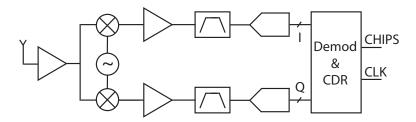

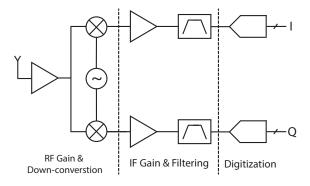

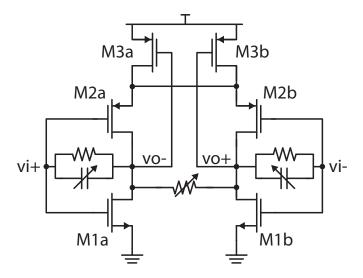

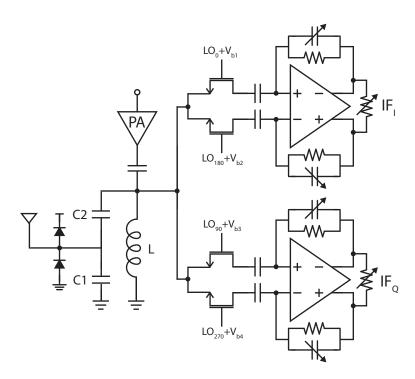

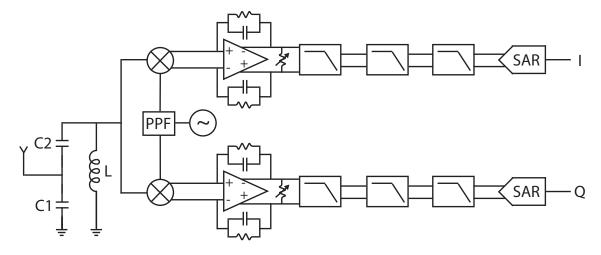

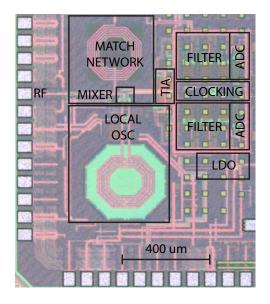

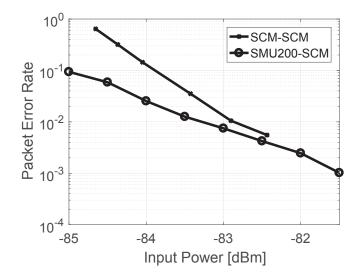

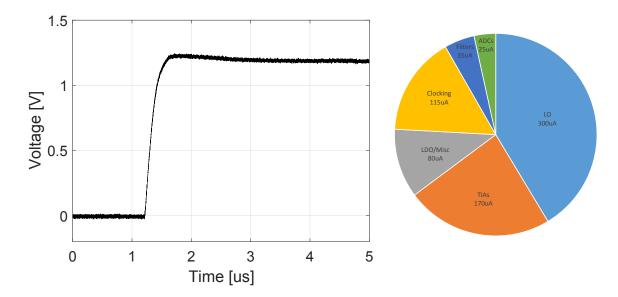

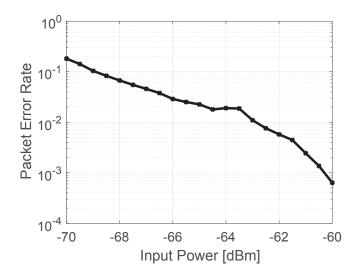

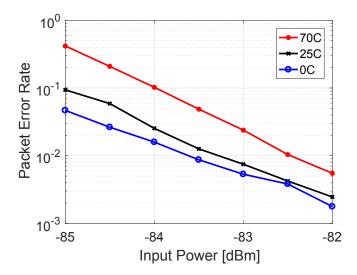

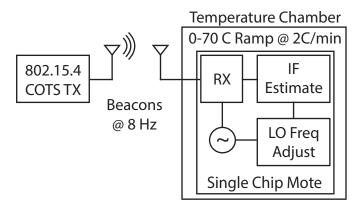

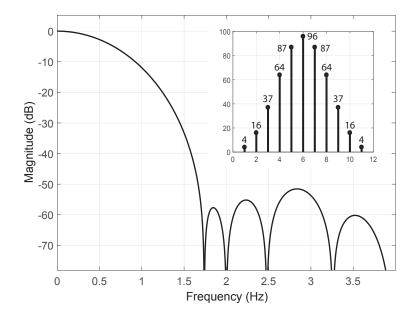

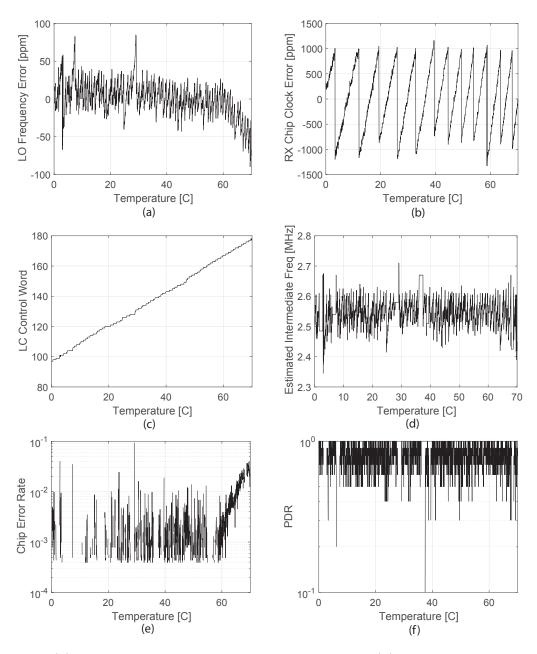

This work implements a crystal-free IEEE 802.15.4 receiver that covers the data path from RF to bits. The receiver utilizes a passive front-end to reduce power and quadrature down-conversion followed by on-chip filtering and digitization. Integrated digital baseband is included for demodulation and clock recovery as well as built-in estimation of the errors in the RF channel frequency and data rate. Initial frequency calibration is performed simultaneously with bootloading using contact-less optical programming. Operation across the 0 - 70 C commercial temperature range has been demonstrated while inter-operating with commercial off the shelf IEEE 802.15.4 devices. The analog portion of the receiver, including the free-running LO, consumes 1.03 mW from a 1.5 V battery while achieving a sensitivity of -83 dBm.

# To Cam

Thanks for putting up with all of this.

# Contents

| $\mathbf{C}$ | ontei                                     | nts                                           | ii |  |  |  |

|--------------|-------------------------------------------|-----------------------------------------------|----|--|--|--|

| 1            | Ove                                       | erview                                        | 1  |  |  |  |

|              | 1.1                                       | The Single Chip Mote                          | 1  |  |  |  |

|              | 1.2                                       | Choosing a Wireless Standard                  | 2  |  |  |  |

|              | 1.3                                       | OpenWSN and Time Synchronized Channel Hopping | 3  |  |  |  |

|              | 1.4                                       | IEEE 802.15.4                                 | 4  |  |  |  |

|              | 1.5                                       | Crystal-Free Challenges                       | 7  |  |  |  |

|              | 1.6                                       | COTS Hardware                                 | 9  |  |  |  |

|              | 1.7                                       | SCM System Overview                           | 9  |  |  |  |

| 2            | Crystal-Free Receiver Design and Modeling |                                               |    |  |  |  |

|              | 2.1                                       | Architectural Decisions                       | 11 |  |  |  |

|              | 2.2                                       | Time Domain Phase Noise Modeling              | 19 |  |  |  |

|              | 2.3                                       | Receiver Design and Modeling                  | 23 |  |  |  |

| 3            | Receiver Analog Design 3                  |                                               |    |  |  |  |

|              | 3.1                                       | RF Frontend                                   | 39 |  |  |  |

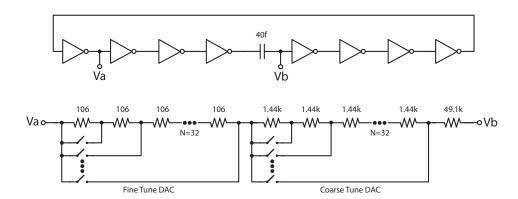

|              | 3.2                                       | Filters                                       | 48 |  |  |  |

|              | 3.3                                       | ADC                                           | 52 |  |  |  |

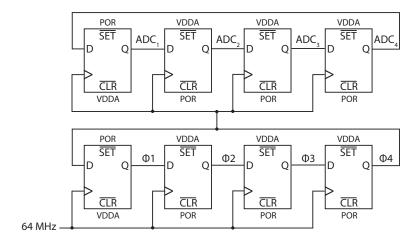

|              | 3.4                                       | Clocking                                      | 56 |  |  |  |

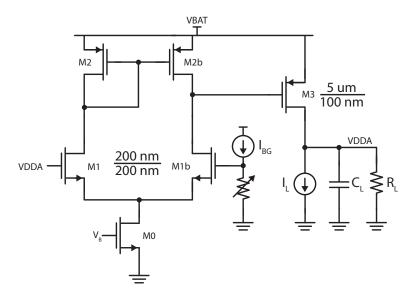

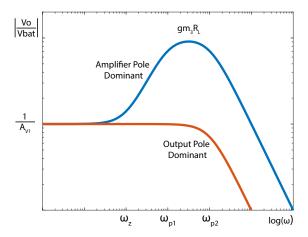

|              | 3.5                                       | Supply Regulation                             | 60 |  |  |  |

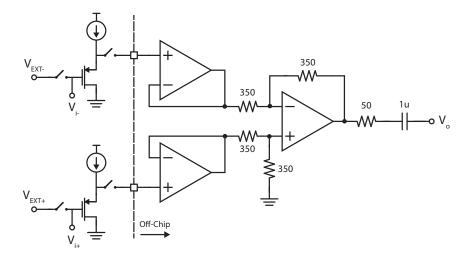

|              | 3.6                                       | Analog Test Harness                           | 62 |  |  |  |

|              | 3.7                                       | Full Receiver                                 | 63 |  |  |  |

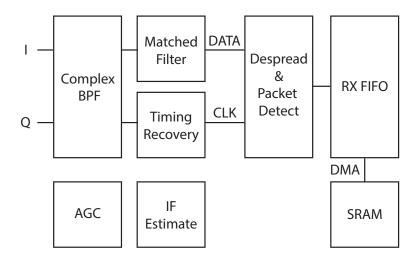

| 4            | Dig                                       | ital Baseband Design                          | 64 |  |  |  |

|              | 4.1                                       | Demodulation                                  | 64 |  |  |  |

|              | 4.2                                       | Clock and Data Recovery                       | 66 |  |  |  |

|              | 4.3                                       | Complex Bandpass Filter                       | 69 |  |  |  |

|              | 4.4                                       | I/Q Mismatch Correction                       | 70 |  |  |  |

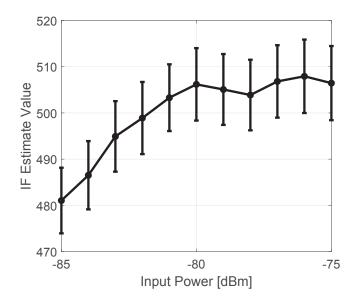

|              | 4.5                                       | Intermediate Frequency Estimation             | 73 |  |  |  |

|              | 4.6                                       | DSSS Despreading                              | 73 |  |  |  |

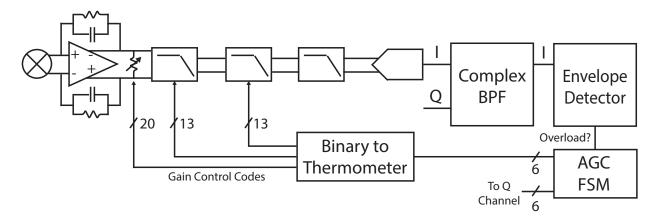

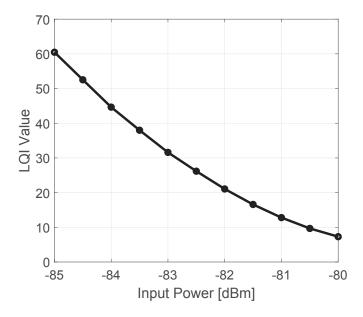

|              | 4.11  | Packet Detection Automatic Gain Control Link Quality Indicator Zero Crossing Counter Demod Arbitrary Receive Mode FPGA Verification | 74<br>76<br>77<br>78<br>80<br>80 |

|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 5            | SCI   | Measurement Results                                                                                                                 | 87                               |

| 0            | 5.1   | Overview                                                                                                                            | 87                               |

|              | 5.2   | RF Frontend                                                                                                                         | 89                               |

|              | 5.3   | Filters                                                                                                                             | 93                               |

|              | 5.4   | ADC                                                                                                                                 | 99                               |

|              | 5.5   | Automatic Gain Control                                                                                                              | 102                              |

|              | 5.6   | Clocks                                                                                                                              | 104                              |

|              | 5.7   | Receiver Performance                                                                                                                | 106                              |

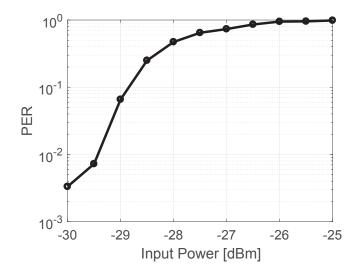

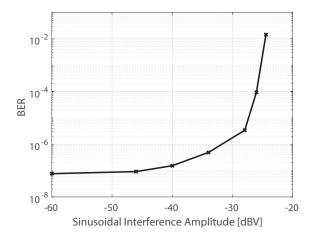

|              | 5.8   | Interference Tolerance                                                                                                              | 109                              |

|              | 5.9   | Power                                                                                                                               | 111                              |

|              |       | Zero Crossing Counter Mode                                                                                                          | 112                              |

|              |       | Baseband Outputs                                                                                                                    | 114                              |

|              |       | Frequency Calibration                                                                                                               | 117                              |

|              | 5.13  | Temperature Tracking                                                                                                                | 118                              |

| 6            | Con   | clusion                                                                                                                             | 124                              |

| $\mathbf{A}$ | MA    | TLAB Phase Noise Modeling                                                                                                           | 129                              |

| В            | Opt   | ical Bootloader Design                                                                                                              | 133                              |

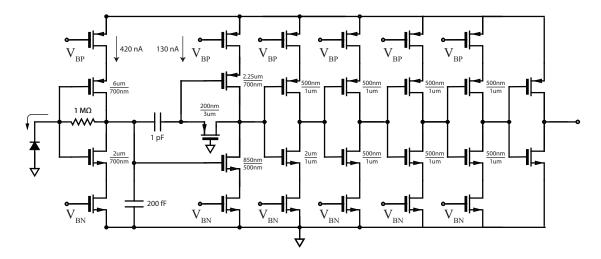

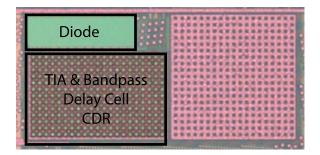

|              | B.1   | Introduction                                                                                                                        | 134                              |

|              | B.2   | System Design                                                                                                                       | 134                              |

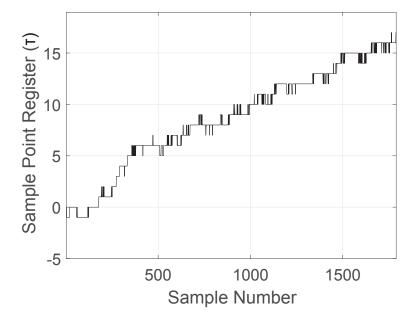

|              | B.3   | Clock and Data Recovery                                                                                                             | 134                              |

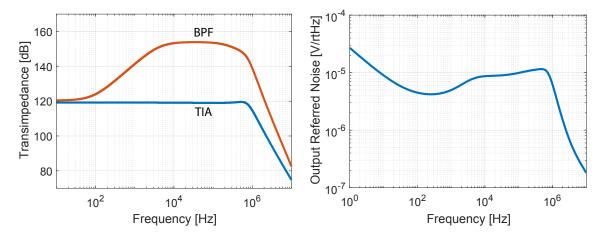

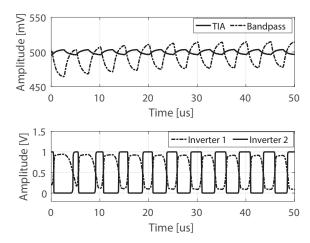

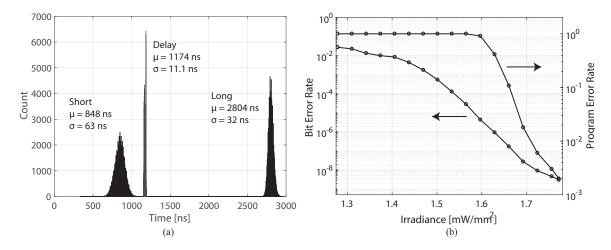

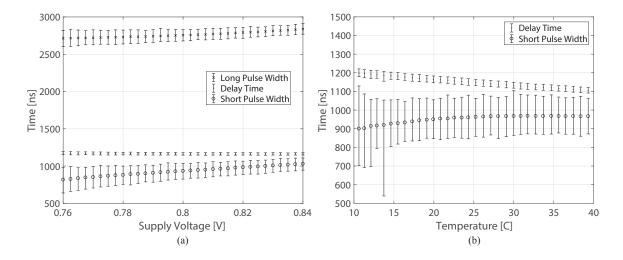

|              | B.4   | Circuit Design                                                                                                                      | 135                              |

|              | B.5   | Digital Backend                                                                                                                     | 137                              |

|              | B.6   | Measurement Results                                                                                                                 | 138                              |

|              | B.7   | Future Iterations                                                                                                                   | 139                              |

| Bi           | bliog | raphy                                                                                                                               | 142                              |

#### Acknowledgments

The Single Chip Mote was an ambitious undertaking for a small academic team and would not have been possible without the contributions of many people. The project never would have made it if the core SCM team of Filip Maksimovic, David Burnett, Osama Khan, and myself had not held together for the five years it took to get here. Fil deserves a shoutout as our fates were intertwined from early on. Rarely is it a good idea to put the success of any part of your project in the hands of another graduate student, but for us I think it worked out better in the end.

Special thanks to my advisor Kris Pister whose relentless optimism and drive got SCM to where it is today (how hard could it be?). Every advisor rolls the dice when they take new students and I'm forever grateful he took a chance on me. Six years later and it still feels like blind luck that I've ended up here. Thanks also to Ali Niknejad for the technical guidance and inspiration along the way.

A tremendous amount of the digital backbone of SCM exists because of the tireless efforts of Sahar Mesri. Thanks to Bob Zhou and Jonathon Wang for all the help with Verilog development and testing. Lydia Lee deserves props for the thankless job of slugging it out with the digital tool-flow setup. The development of the optical bootloader for SCM would not have happened without Andy Ng. A long list of people have contributed in various ways to the testing and development of SCM, thanks to Alex Moreno, Brian Kilberg, Nima Baniasadi, Hall Chen, Paul Kwon, Arvind Sundararajan, and Lorenz Schmid. The feedback of the OpenWSN team and other software developers, Tengfei Chang, Thomas Watteyne, Xavi Vilajosana, and Ioana Suciu was instrumental in steering SCM toward a usable implementation.

Lastly, thanks to the students and staff of both the Berkeley Sensor and Actuator Center and the Berkeley Wireless Research Center. These two organizations are filled with some of the most amazing people I have ever met.

# Chapter 1

# Overview

# 1.1 The Single Chip Mote

This work fits into the broader context of a project called the Single Chip Mote (SCM). The overall goal of this project is to create a low power wireless node that operates with zero external components. This problem essentially distills down to the questions of how to design a radio without a frequency reference, how to integrate an antenna, and how to power the system. The decision was made for this generation of hardware to focus on inter-operation with existing hardware which typically operates in lower frequency bands such as 2.4 GHz. At these frequencies external antennas are still required for reasonable performance. Thus this generation of the Single Chip Mote is intended to operate with two external components, a battery and an antenna. While current hardware is intended to operate from a battery, design consideration is given to minimizing power to enable future operation from scavenged energy sources. Future iterations of the project are likely to address antenna integration by moving to higher frequencies where on-chip antennas become feasible. Note that throughout this manuscript the term crystal-free is used in a manner as to apply to any off-chip frequency reference, whether that be an actual quartz crystal or any other physical resonator such as MEMS.

This project is somewhat unique in an academic setting in that it is very much a system level project aimed at designing a SoC. Not only is the goal to explore the design space of crystal-free radio, but perhaps even more-so, the goal is to produce a mote that can be used in other research projects. The ability to add wireless connectivity where it is previously impossible due to the mass and power requirements of off the shelf hardware enables a significant number of new research possibilities. To qualify as usable, the chip needs to truly operate in a bits-in bits-out fashion with no external components beyond the battery and antenna. Design aspects that might typically be relegated off-chip (like biasing, LDOs, digital implementation on FPGAs, etc) in the interest of increasing the academic rate of publishing cannot be ignored in this case. Thus the project requires a balancing of resources between designing for leading-edge performance and the more mundane aspects of raw func-

tionality. There is simply not the time or personnel in an academic setting to optimize every sub-component. These unique design requirements also demand the contribution of many students, of both graduate and undergraduate experience levels. The Single Chip Mote often demands as much focus on project and personnel management as it does on circuit design.

# 1.2 Choosing a Wireless Standard

There are many architectural possibilities when it comes to designing a low power, crystalfree transceiver. For the purposes of demonstrating academic proof of concept one could simply build a low-complexity proprietary transceiver ASIC, place the non-critical parts offchip on a PCB, conduct error rate measurements, and stop there. While this approach is likely the fastest and most flexible way to explore the fundamental problem, it is the farthest from useful in terms of having a Single Chip Mote for further research work. This option does have the advantage of allowing one to make more optimal architectural choices such as lowering energy/bit or mitigating the impact of performance degradation due to lack of a frequency reference. A major downside to a proprietary communication scheme is that you can only communicate among your own devices without access to existing networks. Deploying transceivers in real-world environments presents many challenges that extend far beyond architectural choices such as carrier frequency and modulation scheme. Managing medium access, networking, and reliable packet delivery are just a few of the many practical problems in creating a usable network of wireless nodes. Rather than try to implement these tasks from scratch it makes considerably more sense to leverage what existing hardware and software has already accomplished in this domain. These considerations lead to a review of current wireless standards for one that is a good target for implementing a network containing many low power crystal-free nodes. While targeting an existing standard simplifies many of the choices in a design, it also imposes specifications that may not be well suited for a crystal-free mote. To facilitate the success of the overall project an emphasis is thus placed on being compatible with existing hardware with less concern on being compliant with every aspect of a given standard.

There are many wireless standards available to choose from due to the rapid expansion of consumer electronics. They can be coarsely divided into the two categories of Internet of Things devices and personal electronics, with some standards arguably encompassing both. Wi-Fi and the 3G/4G/5G cellular standards such as LTE are designed for high performance in a device that has many times over the volume and battery capacity of a Single Chip Mote. While the ubiquity of devices with these types of radios would be a boon to any Single Chip Mote deployment, the advanced, spectrally efficient modulations are ill suited for crystal-free implementation. The IoT class of devices generally have simpler radios and are more focused on lowering power consumption. Examples of popular standards in this class are Bluetooth Low Energy and IEEE 802.15.4. It should be noted that IEEE 802.15.4 here refers to the PHY layer specification and not the sometimes more familiar Zigbee MAC. Both standards employ simple FSK type modulations and are relatively similar in their

overall implementation.

While the hardware implementations of BLE and 802.15.4 transceivers can both be of relatively low complexity and low power, there are still other aspects of the communication system to consider. Simply totaling the page count of the relevant standards declarations for BLE (2822 pages) and IEEE 802.15.4(e) (539 pages) gives an idea of the relative complexity involved in implementing full systems. Not only is it advantageous for the Single Chip Mote project to leverage existing hardware standards, but perhaps even more so it should leverage existing software utilizing these types of radios. Prior to the development of the Single Chip Mote, over a decade of work in this research group has focused on software development tackling the hard problems that exist in wireless sensor networking. One result of that work is a project called OpenWSN [1] which is a standards based, open source software platform that provides IPv6 connectivity to wireless nodes running the IEEE 802.15.4 PHY. Plugging into this existing ecosystem provides an opportunity to very rapidly progress to usable networks once Single Chip Mote hardware is developed. Interoperation with existing hardware platforms that support OpenWSN also provides an opportunity to leverage the capabilities of commercial hardware to bolster the performance of a Single Chip Mote in a network. Ultimately this led to the decision that the main focus of this work would be on implementing a Single Chip Mote that is compatible with off the shelf IEEE 802.15.4 transceivers in the 2.4 GHz ISM band running OpenWSN.

# 1.3 OpenWSN and Time Synchronized Channel Hopping

Two common approaches to medium access in low power wireless networks are wake-up based and time synchronized scheduling (i.e. TDMA). In the general wake-up based approach a low power receiver listens for a signal to tell the device to turn on its main receiver and process an incoming transmission. The goal is to reduce the latency of packet exchange by being free to immediately transmit data as desired instead of waiting for a scheduled opportunity to do so.

The wake-up approach has several drawbacks: 1) In order to consume very little power since it is always on, the wake-up receiver sensitivity is generally much poorer than the main receiver. This effectively limits the overall sensitivity of the device as it will not turn on its main receiver if it didn't hear the wake-up message. 2) If the wake-up receiver is listening on only one channel then it is subject to interference and multipath effects [2]. 3) Without any mechanism to prevent transmissions from occurring at the same time, collisions and contention for medium access become problematic for high density networks.

A Time Synchronized Channel Hopping (TSCH) network attempts to overcome these issues by scheduling communication events. Since the receiver knows when to expect an incoming packet it only needs to be turned on in the proximity of the expected reception and can be left off otherwise. This leads to a very low duty cycle of operation allowing a

higher power and performance receiver to be used for better sensitivity. The low duty cycle scheduled approach also allows for the use of frequency diversity to overcome persistent interference and channel fading. Sequential communication events between two nodes can be scheduled to occur on different channels which has been shown to mitigate these issues [3]. Scheduling also reduces medium access contention between devices that are in the same network and thus cooperating on the same schedule. This reduces the amount of potential collisions to those from other devices in the area on other networks. An often cited downside to the scheduled approach is that the worst case latency bounds can be rather large due to needing to wait for scheduled transmission slots before re-transmitting dropped packets. There are however ways to address these latency issues through diversity and scheduling when the network is built with bounded latency in mind [4] [5].

OpenWSN is an open source implementation of a full, standards-based protocol stack built on IEEE 802.15.4(e) using TSCH medium access which provides IPv6 connectivity to the Internet. It was designed to support multiple hardware platforms and is thus portable to many implementations of 802.15.4 hardware, such as the Single Chip Mote. Given that OpenWSN originated in the same research group it is an obvious strategy to leverage it as the software stack for Single Chip Mote. The implication being that when a working hardware prototype is created, it is a relatively quick process to port the software stack and achieve global IPv6 connectivity on a crystal-free node. The diverse hardware supported by OpenWSN creates the opportunity to intermix nodes of various types and capabilities. For example a handful of COTS nodes could be added to a network of Single Chip Motes to bolster the performance. SCM radios communicating with COTS radios benefit from larger link budgets due to the higher transmit power and better sensitivity of high performance commercial radios.

There is another advantage to TSCH when it comes to adding crystal-free transceivers to an existing network. Due to the scheduled nature of the network, there is a shared sense of time inherent across all nodes in the network. Feedback about discrepancies in expected packet arrival times can be used to correct for clock drifts [6]. Crystal oscillator based wireless nodes already exploit this network feedback to achieve very tight time synchronization of  $< 1\mu s$  [7]. This network-level sense of time can be transferred to a crystal-free mote once it has managed to join the network, either through some initial calibration or search process. Once in the network, the crystal-free nodes sense of time can be compared against the occurrence of scheduled events and used to calibrate free-running oscillators [8].

#### 1.4 IEEE 802.15.4

OpenWSN is built on top of the IEEE 802.15.4 PHY specification [9] and the IEEE 802.15.4(e) amendment that specifies TSCH aspects of the MAC. The standard is aimed at enabling low power communication which is reflected in its relatively lax specifications compared to higher performance standards. The 2.4 GHz OQPSK-HSS PHY is used which provides a 250 kbps user data rate. Direct Sequence Spread Spectrum (DSSS) with an 8:1

| Specification   | Value                     | Tolerance   |

|-----------------|---------------------------|-------------|

| Frequency       | 2.4 GHz - 2.485  GHz      |             |

| Channel Spacing | $5 \mathrm{\ MHz}$        | $\pm 40ppm$ |

| User Data Rate  | 250  kbps                 | $\pm 40ppm$ |

| Chip Rate       | $2~\mathrm{MHz}$          | $\pm 40ppm$ |

| Modulation      | OQPSK-HSS                 |             |

| Sensitivity     | -85 dBm @ 1% PER          |             |

| Interference    | 0 dB/5 MHz + 30 dB/10 MHz |             |

| Max Input Power | $-20 \mathrm{dBm}$        |             |

Table 1.1: Receiver related specifications for IEEE 802.15.4.

spreading is used to provide robustness and improve sensitivity. The relevant specifications are shown in Table 1.1.

The constant envelope nature of the signal allows for the use of a nonlinear PA and simplifies the receive chain. A further simplification of both the transmitter and receiver can be made by recognizing that Offset-QPSK with half-sine shaped baseband data is mathematically equivalent to Minimum Shift Key (MSK) modulation. MSK is a special class of frequency shift key where the data rate is equal to one half of the tone separation. A simple calculation is used to convert an OQPSK-HSS bitstream into its equivalent MSK format as given in [10]. For even indexed chip intervals Equation 1.1 is used whereas an inversion is added for odd chip intervals as in Equation 1.2.

$$k_{even} = I \oplus Q \tag{1.1}$$

$$k_{odd} = not(I \oplus Q) \tag{1.2}$$

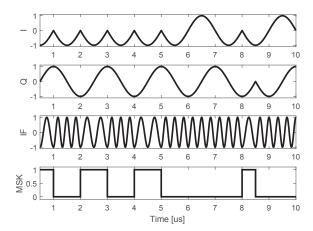

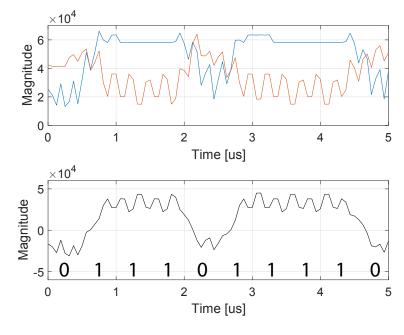

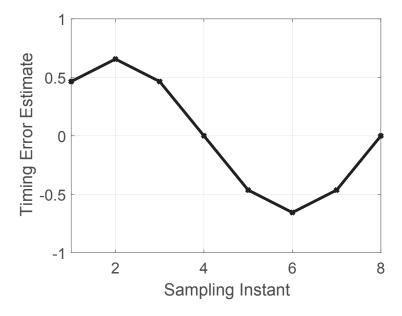

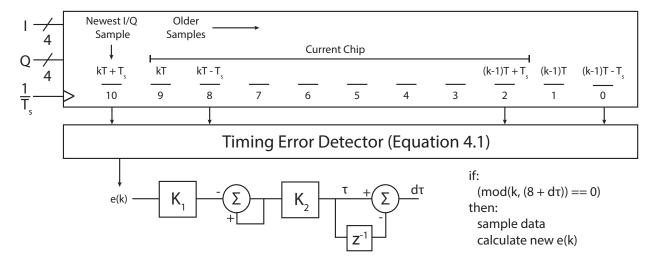

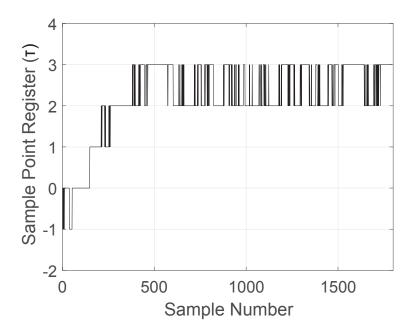

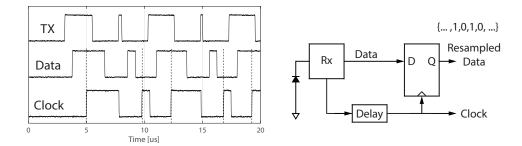

An example of the conversion and corresponding waveforms is shown in Figure 1.1. This conversion is advantageous in that it allows a simpler direct modulation FSK transmitter to be used rather than relying on up-conversion of IQ baseband data. In the receiver this also enables the trade-off of allowing a simpler FSK demodulator to be used, albeit at the expense of reduced performance.

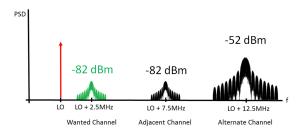

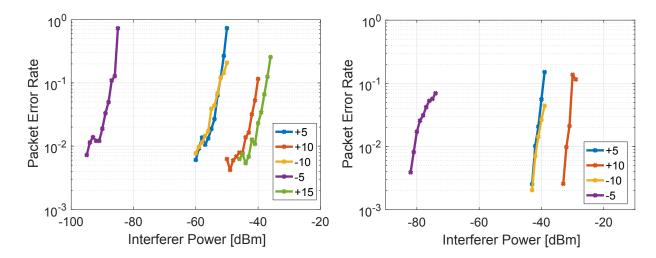

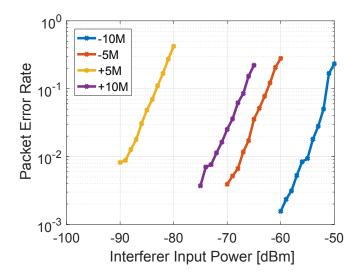

Interference tolerance in IEEE 802.15.4 is specified as 0 dB at the adjacent and 30 dB at the alternate channels (1 and 2 channels away respectively, 5 MHz channel spacing) with the desired signal at 3 dB above minimum sensitivity (i.e. -82 dBm). This is illustrated in Figure 1.2 which depicts an equal power modulated interferer at a 5 MHz offset and a 1000x larger interferer at a 10 MHz offset. In both cases the packet error rate (PER) should not exceed 1% which is also the benchmark for the minimum sensitivity test.

The OQPSK-HSS 2.4 GHz PHY employs Direct Sequence Spread Spectrum (DSSS) coding to improve sensitivity and robustness to interference. Bits to be transmitted are grouped into 4-bit symbols which are then mapped to 32-bit chip sequences. In receive the opposite process occurs using correlators to identify the best symbol match for each 32-bit

Figure 1.1: Equivalence between half-sine shaped IQ data (top) and Minimum Shift Key (bottom).

Figure 1.2: Depiction of interference specifications for IEEE 802.15.4 in a low-IF receiver.

| Preamble    | SFD Length              | Payload        | CRC         |

|-------------|-------------------------|----------------|-------------|

| (8 symbols) | (2 symbols) (2 symbols) | (≤250 symbols) | (4 symbols) |

Figure 1.3: IEEE 802.15.4 packet structure.

chip sequence received. It should be noted that the OQPSK to MSK translation needs to be applied to both the transmitted chip sequence as well as to the correlation sequences used in the receiver. The translation process results in the receiver correlations only needing to be done with 31 bits since each 32nd bit becomes dependent on the symbol that follows it.

The packet structure of a IEEE 802.15.4 PHY later packet is shown in Figure 1.3. A preamble consisting of 8 '0' symbols is translated after spreading to a 256 chip long sequence with a duration of 128  $\mu s$ . The preamble is followed by a one byte Start Frame Delimiter symbol with the value 0x7A. The length field is one byte long with the MSB as a reserved bit. The payload follows the length field and can be a maximum of 125 bytes. At the end of the packet a two byte CRC is appended. Note that the length field includes the two bytes

of the CRC and thus has a maximum value of 127. Due to the detailed steps involved in packet generation (especially the CRC) it is recommended to consult a source such as [11] when attempting to generate valid packets for test purposes.

### 1.5 Crystal-Free Challenges

When attempting to implement a crystal-free 802.15.4 transceiver there are several factors to consider: 1) The RF local oscillator's (LO) ability to tune to a channel 2) The RF LO's impact on modulation accuracy 3) The accuracy and variation of the data rate 4) The accuracy and variation of the scheduling timer.

Without a good frequency reference like a crystal, the free-running oscillators that are responsible for these functions will drift due to noise as well as environmental factors such as temperature. As alluded to in Section 1.4 it is possible to perform periodic corrections on these oscillators using timing information inherent to the TSCH network, but their free-running performance impact still needs to be assessed. The remainder of this section serves to highlight the issues that will be of primary concern when designing a crystal-free radio and that will be discussed throughout this work.

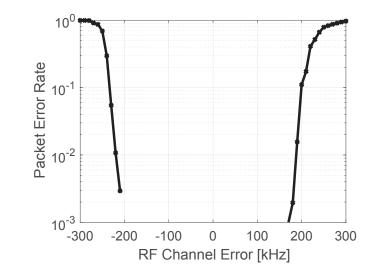

#### RF LO

For the LO, the primary concerns are dealing with signal degradation from phase noise, tuning to the RF channel center frequency, and modulation accuracy. Many of these parameters also vary with temperature which further complicates the design by demanding some temperature compensation mechanism. Even after employing a calibration scheme there will always be some residual error in the RF channel center frequency. While the 802.15.4 standard specifies this allowable error as  $\pm 40$  ppm, COTS receivers were found to implement a tolerance greater than this as seen in Section 1.6. The receive chain and demodulator in the Single Chip Mote should take this error source into account and be tolerant of it as well. Regardless of any periodic corrections to its center frequency, a free-running RF LO is also going to have significantly higher phase noise than a PLL-based synthesizer in a typical transceiver. The system-level impact of this increased phase noise is of significance interest when designing a crystal-free radio and discussed in depth in Section 2.2. The modulation accuracy of the transmitter is not only affected by phase noise, but also by the choice to implement the modulation as Minimum Shift Key. The tone spacing used in the modulation will have some error which will degrade the error vector magnitude of the modulated signal. The effects of this tone spacing error on the receiver are similar to those of phase noise and RF channel accuracy and can thus be modeling in a similar manner.

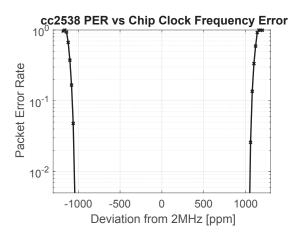

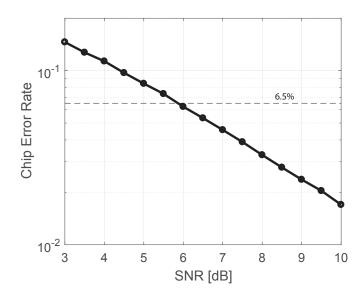

Figure 1.4: Error rate vs chip clock center frequency inaccuracy for the cc2538.

#### Chip Clock

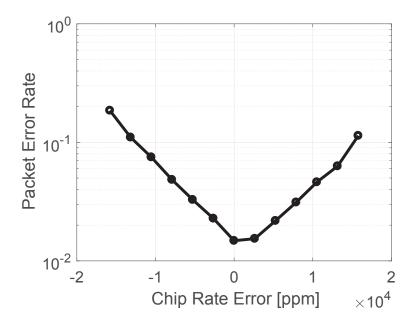

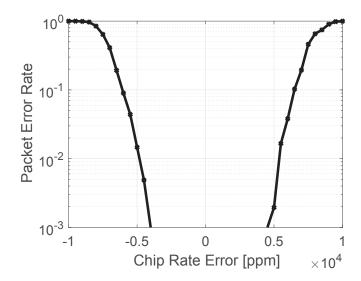

IEEE 802.15.4 specifies a chip rate of 2 MHz with a tolerance of  $\pm 40$  ppm, which dictates a high quality source for this clock. In the absence of a crystal the highest quality on-chip clock available is the RF LO. While a divider could be used to generate this chip clock from the RF source, it is not a desirable situation from a power perspective. Furthermore the RF LO suffers from temperature effects that require calibration before an accurate 2 MHz clock could be derived. It was found that commercial receiver's tolerance on this clock rate are well in excess of the value specified by the standard. This enables the Single Chip Mote to use a lower power, lower quality clock source and still communicate with other 802.15.4 hardware. Since the receiver clock recovery for SCM is under our control, chip clock rate tolerance is a design parameter that should be considered.

### Sampling Clock

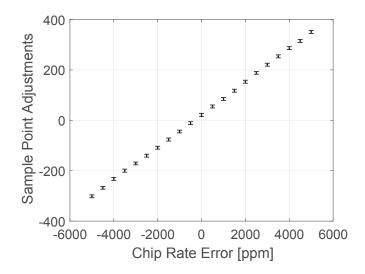

While in the transmitter the chip clock exists as its own independent oscillator, in the receiver the chip clock is derived from the ADC sampling clock. A typical receiver oversamples the incoming data stream at a rate which is an integer multiple of the data rate. This gives the receiver multiple samples per symbol with which to perform functions like demodulation, clock recovery, etc. If the sampling clock of the receiver is inaccurate or varying, then so is the chip clock. Whether the inaccuracy originates in the transmit or receive chip clock is indistinguishable in terms of performance. The receiver clock and data recovery must be designed with tolerance of chip clock inaccuracies in mind.

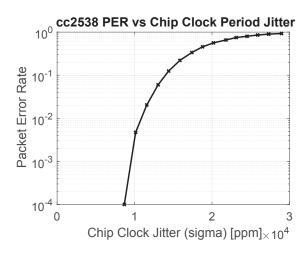

Figure 1.5: Error rate vs chip clock jitter for the cc2538.

#### 1.6 COTS Hardware

As previously mentioned there are a variety of hardware options for IEEE 802.15.4 that OpenWSN already supports. The TI CC2538 is used in the OpenMote [12] and is thus a good candidate for inter-operation with the Single Chip Mote. It is of interest to investigate the response of this SoC to the types of errors introduced by a crystal-free system in order to determine the limits of crystal-free operation. The datasheet [13] for this part specifies that it will tolerate an RF channel error of  $\pm 150$  ppm and a chip clock error of  $\pm 1000$  ppm. Since the chipping clock is of particular interest, measurements were taken to confirm these values as well investigate the tolerance to jitter on the chipping clock are shown in Figures 1.4 and 1.5.

### 1.7 SCM System Overview

In general this work aims to implement a receiver that meets the relatively modest standards set forth by IEEE 802.15.4, do so without using a crystal reference, and to consume as little power as possible. The required sensitivity of -85 dBm allows for a relatively high noise figure which reduces the power requirements of the receiver. Combined with a low power transmitter output power of -10 dBm and assuming a few dB of antenna loss on both ends still results in a link margin in excess of 70 dB. While range is very dependent on the antennas used and the propagation environment, with this link budget one could expect 1-10 m indoor range and 10s of meters outdoors. If the RF link is between a Single Chip Mote and a commercial IEEE 802.15.4 transceiver, then an additional 10-15 dB of link margin is gained by the higher output power and better sensitivity of the high performance COTS device. The interference tolerance of the mote is another area where power can be saved

at the expense of performance. Linearity costs power, and the system level approach taken here is to allow the network to re-transmit packets that are dropped due to interference rather than spending considerable amounts of power to reduce the chances of problems due to interference.

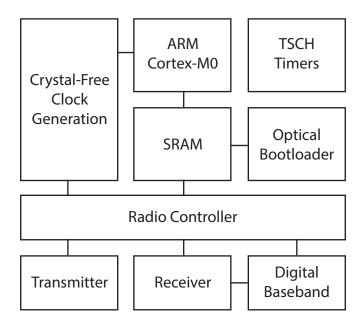

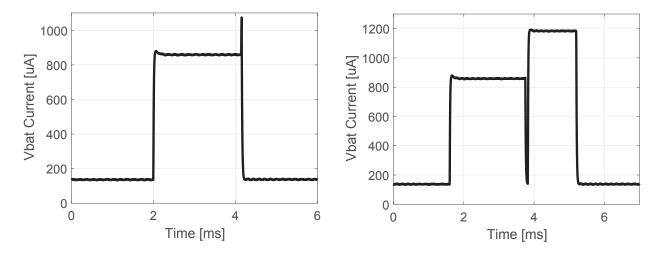

The Single Chip Mote is built around an ARM Cortex-M0 microprocessor with 128 kB of SRAM equally split between data and instruction memory. The instruction memory is programmed via an on-chip optical receiver as discussed in Appendix B. Dedicated hardware FSMs were developed to support IEEE 802.15.4 transmit/receive actions independent of processor control. A bank of dedicated TSCH timer interrupts trigger the radio actions and DMA provides direct movement of packets to and from SRAM. A detailed guide to the digital system is given in [14]. Integrated power management includes multiple LDO voltage regulators referenced to a programmable fractional bandgap. A variety of freerunning clock sources are integrated to serve the functions of RF LO, chipping, sampling, and system clocks. A flexible bank of counters and dividers are also included to accommodate various calibration schemes between these oscillators. The remainder of this work focuses on the receiver implementation, which encompasses everything from EM waves reaching the antenna to packets being delivered to the application layer. The design of the frontend, down-conversion, filtering, and digitization are covered in Chapter 3 while the digital baseband is discussed in Chapter 4. Chapter 5 presents measurement results for the overall receiver.

# Chapter 2

# Crystal-Free Receiver Design and Modeling

Even after narrowing down to focus on an IEEE 802.15.4 transceiver there is still a tremendous amount of flexibility in implementation. The design is even further confounded by considering the complications added by crystal-free operation.

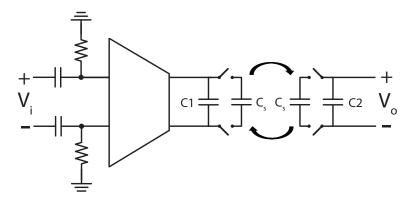

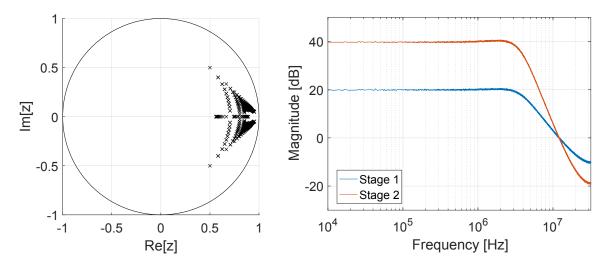

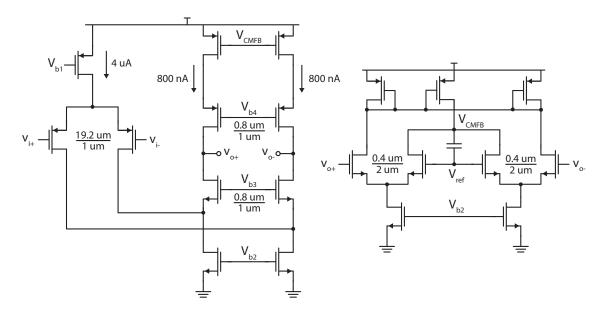

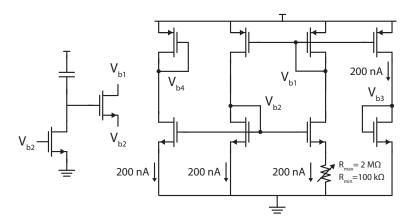

The design considerations here will be subdivided into two circuit domains: analog (how to get from RF to bits) and digital (turning those bits into packets). There is a considerable amount of flexibility in where to draw the boundary between these analog and digital portions. Process scaling has made it attractive to push as much signal processing as possible into the digital domain at the expense of increasing the performance demands on the ADC. This work targets a 65 nm process in which digital processing operating in the 10s of MHz range can consume a significant fraction of the overall system power. Therefore a very complex digital baseband approach is not likely to yield the lowest power system solution. It is difficult to analyze this trade-off between analog and digital in advance since detailed power estimates for digital blocks generally require them to have already been written and synthesized. The approach taken here is to balance the design between analog and digital by placing signal down-conversion and the bulk of filtering in the analog domain, with the digital domain containing further filtering, demodulation, and clock and data recovery (CDR).

The remainder of this chapter focuses on the early stages of a design where there are primarily two tasks to complete: 1) Make architectural decisions that best support the system level goals required by the receiver. 2) Model the receiver performance in the face of these decisions in order to set circuit level specifications.

### 2.1 Architectural Decisions

A receiver implementation can be broadly broken down into three steps: 1) down-convert the signal from the RF carrier used for transmission 2) perform signal filtering and digitization and 3) recover the payload information that was encoded in the data stream.

These steps involve a series of design choices which may seem rather arbitrary at the time they are made but are inextricably linked in the overall system. The goal is to make the best educated choices possible in a timely manner, then re-evaluate them later as the design complexity increases and the trade-offs are better understood. This approach helps to avoid slowdowns caused when the number of seemingly free parameters makes the design space appear paralyzingly complex. There will never be enough time to optimize every last parameter, and the functionality of the entire Single Chip Mote system will be prioritized over block level performance.

#### **Down-Conversion**

#### Phase Coherence

The first choice to be considered is whether to do coherent or non-coherent down-conversion. For an FSK demodulator there is approximately a 2.5 dB theoretical difference in the required  $E_b/N_o$  for demodulation between the two. Obtaining this extra performance however requires a carrier tracking loop to estimate the phase of the incoming signal which adds extra design time, complexity, power, and points of failure. The use of free-running oscillators with moderate amounts of phase noise will also degrade the ability of a tracking loop to estimate the carrier phase and thus the entire performance gain is unlikely to be realized in a crystal-free radio. Given the costs to implement what is likely to be a small benefit a non-coherent architecture was selected.

#### **Local Oscillator**

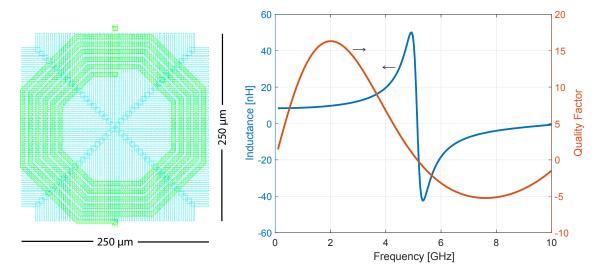

There are two categories for fully on-chip free-running oscillators which can be used as the RF LO (local oscillator). The first is resonant oscillators which use an LC tank to produce an oscillation at a specific frequency. The second is ring oscillators which are constructed from delay elements placed in a loop. It is shown in [15] that for a ring oscillator to achieve the same phase noise performance as an LC tank it requires more than  $Q^2$  times the current, which clearly makes the LC preferable from a low power standpoint. There is still some argument to be made in favor of the ring oscillator if area is of substantial concern. The size of the inductor in the LC tank for a 2.4 GHz LO is in the nH range and will measure 100s of  $\mu m$  on a side, which does not change with process scaling. While the ring oscillator itself can be much smaller, its poorer performance and sensitivity require a substantial amount of circuitry for supply conditioning and tuning which will reduce the area benefit. Measurement results on free-running oscillators also show frequency stability issues that appear related to flicker noise which are substantially worse than an LC tank [16].

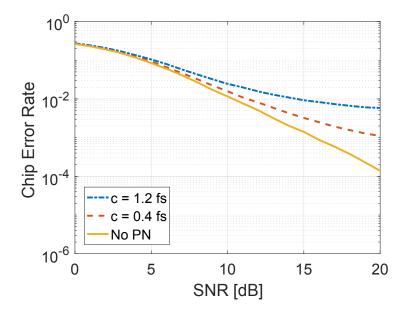

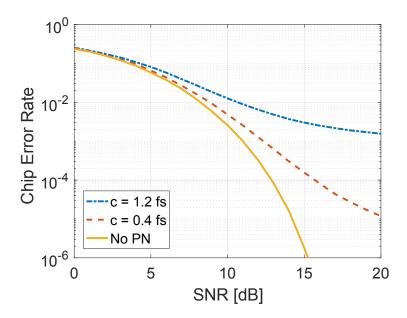

Given these considerations an LC tank oscillator is chosen as the LO for the Single Chip Mote, and the circuit level design is discussed extensively in [17]. This work is primarily only concerned with the LO insofar as its phase noise affects receiver performance. Circuit

simulators provide performance data related to phase noise on a given LO implementation, but are too slow to evaluate entire systems over the span of many packets which is required for statistical performance verification. System level behavioral modeling approaches are a much faster way to perform this verification, but may not support time domain behavior of a noisy oscillator. What is needed is a way to bridge the gap and implement behavioral system level models with the phase noise behavior predicted by circuit level simulations. This approach will be discussed in further detail in Section 2.2.

#### Direct Conversion vs Low IF

After having decided on a non-coherent receiver using an LC tank LO the next decision involves the frequency plan for down-conversion. Direct conversion receivers use an LO that is at the same frequency as the RF carrier and shift the modulated signal down to baseband for further processing. While this eliminates the image problem and its corresponding filter requirements found in heterodyne receivers, it introduces a few other problems. Since the signal is now centered at DC, any offsets within the receive chain must be reduced or eliminated without affecting the integrity of the desired modulation. Any DC tracking loop introduced for this purpose is also going to require additional power and design time. Flicker noise from signal processing circuits may also be significant in the frequency region occupied by the baseband signal.

An alternative is the low intermediate frequency (IF) topology where the signal is shifted down to a carrier of a few MHz. By choosing the IF above the flicker corner both noise and DC offset can be removed without affecting the signal. This approach comes at the cost of increasing the power consumption of the signal processing chain as it needs to operate at higher frequency than the baseband data rate. The rejection of image band frequencies also becomes a concern.

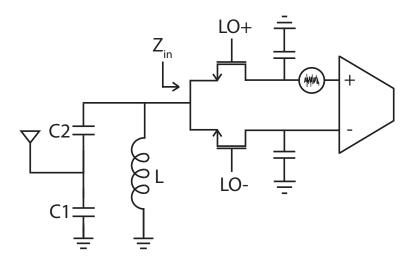

In either case LO pulling can be a concern for high input powers. IEEE 802.15.4 specifies the maximum signal input power as -20 dBm, which after RF gain can cause significant pulling or even injection locking of the LO. One possible solution is to implement the LO at twice the desired channel frequency and divide it by two. This avoids the pulling issue but the divider logic can consume significant power, especially in a 65 nm process. Another problem that affects either architecture choice is frequency offset from the desired RF channel center frequency. This error can be lessened through system level approaches as discussed in Section 5.13, but will never be eliminated and should thus be considered when evaluating demodulator performance. To target low power and low complexity it was decided to utilize a low IF architecture using an LO at 2.4 GHz for the Single Chip Mote.

### Filtering

The two main tasks required of the receive filter are to limit the noise bandwidth of the signal and to remove interference. Disregarding interference for a moment, the choice of what bandwidth to use for the filter involves trade-offs between signal power, noise power,

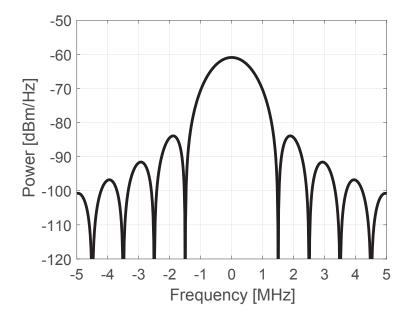

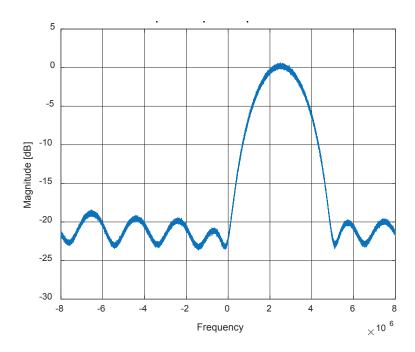

Figure 2.1: Spectrum of an MSK modulated signal with 2 MHz data rate.

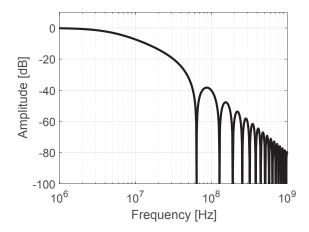

and inter-symbol interference. The spectrum of an MSK modulated signal is shown in Figure 2.1. While the null-to-null bandwidth is 1.5 times the data rate, 99% of the signal power is contained in a bandwidth of 1.2 times the data rate. A wider filter bandwidth captures more of the signal power but also lets in more noise power. Too narrow of a bandwidth will not only reduce both the signal and noise power, but will also begin to cause inter-symbol interference. When the overall system performance is considered the optimum bandwidth is dependent on many factors, and for initial design considerations is chosen here to be equal to the data rate of 2 MHz.

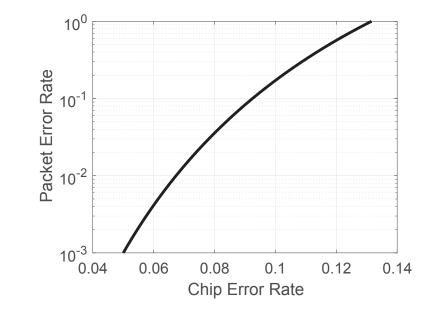

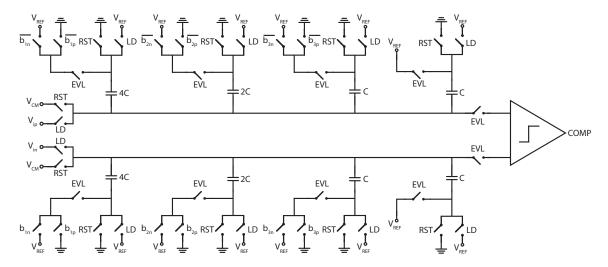

The steepness of the filter roll-off is not especially critical for noise considerations since as filters increase above third order there are only relatively small changes in equivalent noise bandwidth. The roll-off is however of critical concern when it comes to removing unwanted interference signals at various frequency offsets. IEEE 802.15.4 does not specify an especially stringent set of interference requirements as outlined in Section 1.4. To reiterate those requirements here, a < 1% packet error rate should be maintained for a -82 dBm desired signal while 1) a -82 dBm modulated interferer is present 5 MHz away on the adjacent channel and 2) a -52 dBm modulated interferer is present 10 MHz away on the alternate channel. A system level model can be used in order to validate that these conditions are met for a given filter within the overall system. The model used for evaluating these filter requirements in discussed in Section 2.3 and the actual circuit implementation is discussed in Chapter 3.

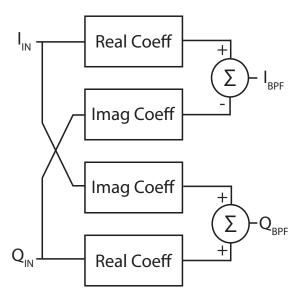

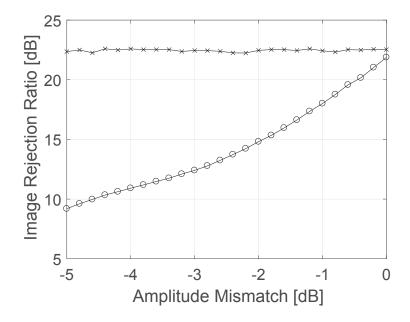

#### **Image Rejection**

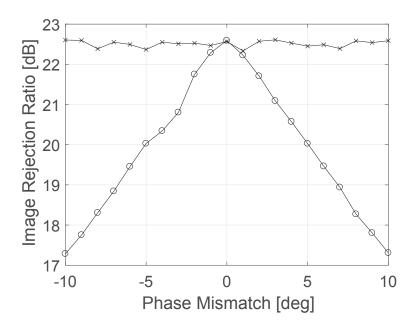

In addition to the filtering requirements imposed by the standard there are additional requirements introduced by the choice of a low IF architecture. While the choice of an IF in the low MHz range is a reasonable trade-off between avoiding flicker noise and limiting bandwidth requirements in the filter, it potentially causes the image band to lie in the adjacent or alternate channels. IEEE 802.15.4 specifies no image rejection requirements, so the standard adjacent/alternate channel rejection values will be applied here. The image rejection can be accomplished in either the analog domain using image reject mixers or digitally using complex bandpass filters. In either case the amount of rejection that can be achieved is limited by the amplitude and quadrature phase accuracy of the local oscillator signals. The extent to which the rejection is compromised can be analytically described for the analog rejection approach but other factors come into play with a digital complex bandpass filter. The factors are those that influence the nominal stop-band rejection at the image frequency and include the number of taps in the digital filter and quantization effects. The digital complex bandpass approach is adopted for the Single Chip Mote and is discussed further in Chapter 4.

There are several ways that the required quadrature LO signals can be generated, each with its own advantages and disadvantages. One option is to use CMOS logic to create phase shifted LO signals with varying duty cycles. Depending on the process used this logic operating at RF can consume significant power. If a divide by two LO architecture is already being used then it can be combined with the quadrature generation. Quadrature signals can also be generated by locking two separate oscillators into a quadrature relationship. This requires doubling the power consumption by essentially having two LOs. A third option is to place a passive polyphase filter between the LO and mixer to generate the required phase shift. This is the approach taken for the Single Chip Mote and the RC implementation is discussed in [17]. There is some amplitude loss across the passive network so more current must be used in the LO to reclaim the lost swing, but this is still the most attractive solution in this 65 nm process node. Correcting for quadrature inaccuracies due to process mismatch in the passive polyphase is difficult due to the small component values used in the filter. Rather than attempting to implement correction approaches in the analog domain with components operating at RF, a digital approach can be used to correct for quadrature inaccuracy in the digital domain [18] and is discussed further in Chapter 4. It should also be noted that by filtering out the image channel a 3 dB improvement in SNR is obtained by effectively halving the amount of thermal noise within the receiver's bandwidth. This 3 dB increase in SNR does not come for free however as image rejection requires I and Q channels which doubles the power consumption. The same SNR improvement could be obtained by spending twice the power in the I channel alone, although image rejection is then lost completely.

#### Demodulators and Packet Acquisition

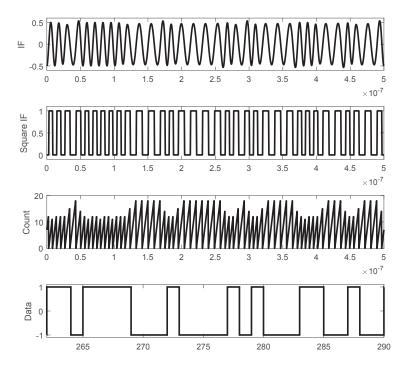

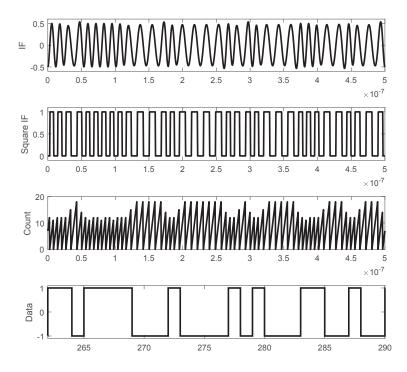

There are many MSK demodulation schemes of varying complexity and performance. Two of these methods are implemented in the Single Chip Mote and are briefly introduced here. A more detailed discussion on demodulators and digital baseband can be found in Chapter 4. The first demodulator is a very straightforward implementation of an FSK demodulator which will be referred to as the Zero Crossing Counter (ZCC). The ZCC attempts to discriminate between the two modulation tones by measuring the timing between successive zero crossings in the IF waveform. This can be done by sampling the IF waveform at a high rate and counting how many clock cycles occur between successive zero crossings. A threshold on the count value then yields an estimate of whether the IF was the fast or slow FSK tone as shown in Figure 2.2. A high sampling frequency is required to obtain the necessary resolution between count values for the two tones. It is also advantageous to use as low of an IF center frequency as possible since that increases the count ratio between the two tones given that their spacing is fixed at 1 MHz.

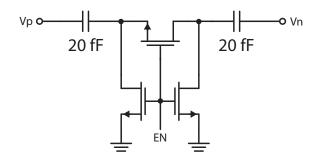

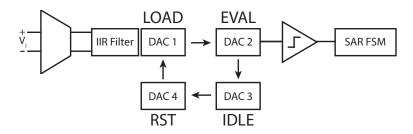

The ZCC benefits from only requiring a single bit input from a comparator rather than a full multi-bit ADC. Since this demodulator operates solely on a real-valued IF signal, the receiver can also save power by shutting down its quadrature receive path at the expense of image rejection. Additional filtering could be digitally implemented on the 1-bit comparator output prior to the ZCC demodulator, but this is not done in the Single Chip Mote to reduce complexity. The simplicity of the ZCC is not without its drawbacks. Since zero crossings are the method of demodulation the ZCC requires relative strict duty cycle control to avoid corrupting the FSK information. This translates into a strict offset limit on the comparator, which means an offset calibration loop is likely required. The ZCC performance is also inhibited by the location of zero crossings relatively to bit boundaries. With no carrier recovery mechanism in the receiver there is no guarantee that bit transitions occur at the zero crossings of the IF. When the modulation changes in the middle of a count value the demodulator is more likely to incur errors. With no way to know or correct either the transmitter or receiver LO phase then the average performance of the ZCC must be evaluated across a uniform random distribution of  $2\pi$  for the LO phase.

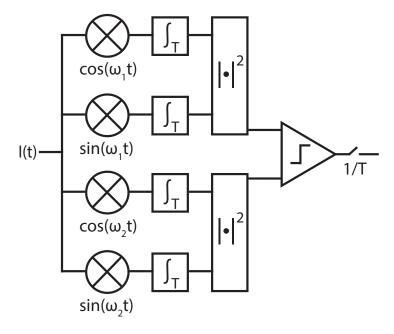

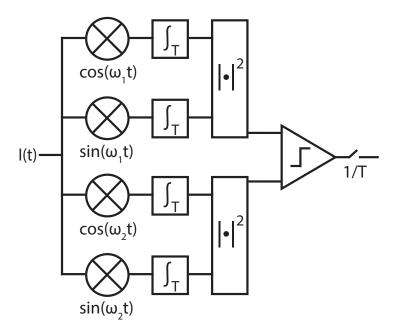

The second demodulator implementation is based on matched filtering, which is known to provide the optimal demodulator for non-coherent FSK [19]. As shown in Fig 2.3, templates for the two FSK tones are correlated with the incoming signal and the magnitude of their output is compared. Whichever template has a higher correlation value is considered the better match and that data bit is then selected for output. Since carrier phase is not known, quadrature templates are used so that the phase of the incoming IF waveform is irrelevant. Ideally the two filter templates are orthogonal for the best selectivity, but this is not always possible, as is the case here since the 1 MHz tone separation is not a free variable to be modified.

Convolution with the matched filter templates is effectively implementing a digital bandpass filter centered around each of the modulation tones and thus leads to inherently better selectivity than the ZCC approach. The matched filter can also be operated with lower sam-

Figure 2.2: Transient waveform of zero crossing counter demodulator behavior. At every zero crossing of the IF waveform, both rising and falling, the counter is reset to zero. If the counter exceeds a threshold then the output bit is deemed a '0' otherwise if the count value remains below the threshold the output is '1'.

ple rates as there is no longer the requirement to differentiate between small time intervals. A drawback of the matched filter demodulator over the simpler ZCC is the requirement for a multi-bit input, which can complicate the design space by now requiring a more complex ADC. Clock recovery is another very important part of the receiver following the demodulator and will be discussed in depth in Chapter 4. For now CDR performing near its ideal limit will be used for system modeling. Further details on demodulator implementations are also discussed in Chapter 4.

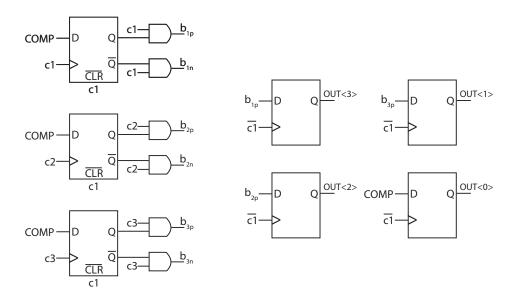

#### Despreading

All steps following CDR utilize the work implemented in [14] and will be summarized here as this work is concerned with the entire data path from antenna to packet storage in memory. The process of converting received chip sequences back into symbols is done via a bank of correlators. Each set of 32 received chips is compared against the 16 possible sequences outlined in [9] and the best match is selected based on smallest Hamming distance. Note that since the transceiver is being implemented as MSK the values used in the correlators are the MSK transformed versions rather than the OQPSK ones defined in the standard. Single

Figure 2.3: Block diagram of the matched filter demodulator for non-coherent FSK.

Chip Mote utilizes hard decisions to minimize the correlator complexity but implementing soft decisions using multi-bit output from the demodulator could improve the performance by approximately 2 dB [20]. There also exists an opportunity to exploit the cyclically shifted nature of the different chip sequences to simplify the correlator hardware implementation if desired [21].

#### Packet Acquisition

After bits have been recovered there is still the task of temporally locating the start of the packet in the presence of noise and interference. IEEE 802.15.4 contains both a preamble and a start frame delimiter (SFD) for this purpose as discussed in Section 1.4. Both [14] and [13] implement packet detection by first searching for some number of preambles followed by the SFD. An adjustable threshold is used for how many errors are acceptable in these correlations. There is a trade-off to be made here in how sensitive the packet detection mechanism is. If the receiver accepts matches with high error rates then it is less likely to miss a packet, but is more likely to falsely trigger on noise. If instead the receiver requires a very accurate match before it will begin storing packet data then it will miss many packets near its minimum detectable signal level. How long the receiver will be listening to random noise before the packet is expected to arrive also plays a role. If the time between when the receiver is turned on and when the packet actually arrives is very short, as say in a very tightly time synchronized TSCH network, then the receiver can afford to relax its threshold settings

Figure 2.4: Exaggerated example of phase deviation due to noise.

since there are simply fewer opportunities for false triggering. Given this set of trade-offs, it is imperative that as much control over this detection process be given to the application software as possible to allow for optimizing the detection for the situation. Consideration should also be given to the mechanism for aligning the boundaries of the 32-bit long chip sequences that are fed into the correlators. Ideally the receiver is able to investigate possible alignment matches while simultaneously monitoring for better matches in order to reduce acquisition errors.

### 2.2 Time Domain Phase Noise Modeling

Understanding how the phase noise of an open loop oscillator affects transceiver performance is critical to the design of a crystal-free radio. The effect of phase noise on a receiver is heavily dependent on the communication protocol and the specifics of implementation. Therefore it is desirable to develop a behavioral model of the complete system in order to derive circuit level specifications. There are many ways to simulate transceiver performance, each with its own advantages and disadvantages. For this work MATLAB was chosen as the system level simulator due to its flexibility. In order to implement a time domain behavioral model assessing the impact of phase noise, it is necessary to understand how to generate discrete-time sequences which mimic the behavior of a free-running oscillator.

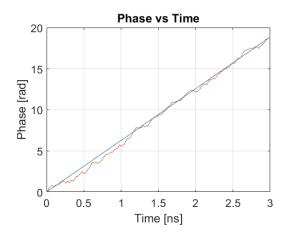

An ideal oscillator linearly accumulates phase over time whereas any real oscillator will have perturbations in its phase due to noise. An exaggerated depiction of this is shown in Figure 2.4. In the time domain this variation appears as a random variation in frequency known as jitter. In the frequency domain it results in a spreading of power across a range of frequencies resulting in what are often termed "skirts" when viewed on a spectrum analyzer. There is extensive literature already discussing the mechanisms and mathematics of phase noise [22] [15]. The goal of this section is not to provide an exhaustive tutorial on phase

noise, but rather to provide an overview on generating time domain sequences that can be used to model the impact of phase noise on a receiver.

A generic oscillation with phase noise can be expressed as shown in Equation 2.1 where  $\phi(t)$  represents a random fluctuation in phase. There can be multiple power law noise processes present in  $\phi(t)$  although oscillators of interest predominately consist of white and flicker noise.

$$x(t) = \cos(\omega t + \phi(t)) \tag{2.1}$$

A discrete time representation of  $\phi(t)$  that accurately captures its spectral properties is required in order to generate a time series for simulation in MATLAB. The required discretization can be obtained from [23] [24] and is given in Equation 2.2. The frequency of oscillation is  $f_0$ , w(n) is a random variable with Gaussian distribution,  $\Delta t$  is the simulation time step, and c is a scalar constant that represents the rate at which the phase variance grows due to white noise.

$$\phi_w(k) = 2\pi f_0 \sum_{n=0}^{k-1} w(n) \sqrt{c\Delta t}$$

(2.2)

It is shown in [22] that the power spectrum of an oscillator in the presence of only white phase noise is Lorentzian in shape and is described by Equation 2.3. This is the single sided power spectral density and  $f_m$  represents the frequency offset from the center frequency of oscillation  $f_0$ . It should be observed that a single scalar constant is sufficient to describe both the time domain properties of the generated  $\phi(k)$  sequence as well as the resulting power spectrum of the oscillation.

$$\mathcal{L}(f_m) \approx 10 \cdot \log_{10}\left(\frac{f_0^2 c}{\pi^2 f_0^4 c^2 + f_m^2}\right) \tag{2.3}$$

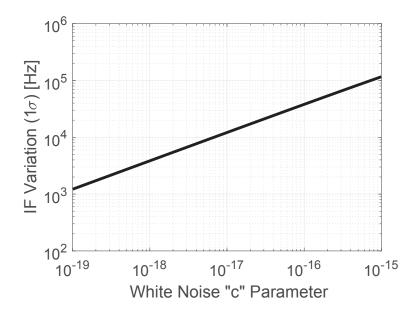

The constant c has further intuitive physical meaning as it also describes the cycle-to-cycle jitter of the oscillation as given in Equation 2.4. Since a low-IF receiver architecture is being designed it is also of interest to know how the cycle-to-cycle jitter of the RF oscillator will translate to jitter of the intermediate frequency after down-conversion by a mixer. This translation is given in [25] and is shown in Equation 2.5. This simple set of equations now provides a very useful link between circuit and system level simulations. Error rate simulations can provide specifications on the value of c which can be extracted from transistor-level simulations to assess a potential oscillator.

$$\sigma_{RF}^2 = \frac{c}{f_0} \tag{2.4}$$

$$\sigma_{IF}^2 = \sigma_{RF}^2 \cdot (\frac{f_0}{f_{IF}})^3 \tag{2.5}$$

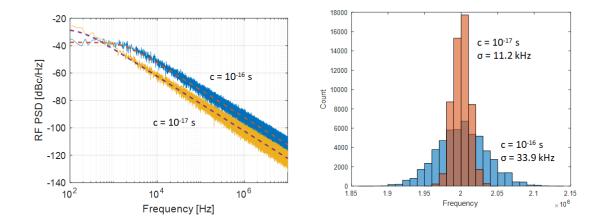

Figure 2.5: Left: PSD with white phase noise values of c=1e-17 and c=1e-16 s. Right: Histogram of variation at IF.

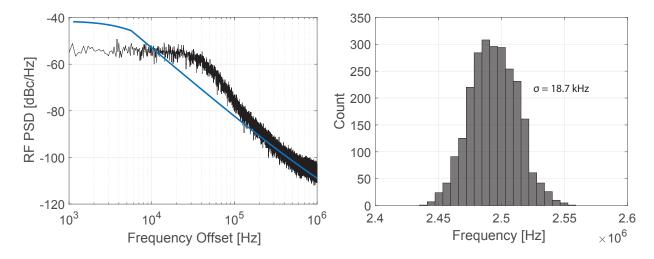

Figure 2.5 shows two example oscillators with different values of c and their corresponding distributions of cycle-to-cycle jitter after mixing down to an IF of 2 MHz. Note that in both cases the frequency variation due to the white phase noise is significantly smaller than the 1 MHz  $\Delta f$  tone spacing used by the IEEE 802.15.4 MSK modulation.

The above treatment of phase noise only considered the impact of white noise. Depending on the design of the oscillator and communication system it may also be important to assess the impact of flicker noise. This work will follow the approach used in [23] which is given in Equation 2.6. Another constant denoted  $c_f$  is used to describe the magnitude of the flicker noise component and  $w_f(n)$  is another Gaussian random variable (distinct from the random variable used for white noise). In order to generate a sequence that has the appropriate spectral properties of flicker noise, h(k) is generated based on a recursive fractional differencing approach as given in [26] and shown in Equation 2.7. This approach can be used for various power law noise processes by choosing the value of  $\beta$ , which for flicker noise is  $\beta = -3$ . It should be noted that the required convolution operation imposes a heavy computational burden for long time domain simulations. For simulations of extended duration it becomes imperative to compute this convolution using the FFT rather than doing so in the time domain.

$$\phi_f(k) = 2\pi f_0 \cdot \Delta t \sqrt{2\pi c_f} \sum_{n=0}^{k} (h_{k-n} \cdot w_f(n))$$

(2.6)

$$h(k) = (k - 1 - \frac{\beta}{2}) \cdot \frac{h_{k-1}}{k}$$

where  $h(0) = 1$  (2.7)

The overall equation for generating a discrete-time representation of an oscillator with both white and flicker phase noise is shown in Equation 2.8. The spectrum is no longer

Figure 2.6: Left: PSD with white and flicker noise. Right: Histogram of variation at IF.

described by a Lorentzian profile, but it is still possible to extract values for c for  $c_f$  based on curve fitting for comparison to transistor-level oscillator simulations. This can be accomplished by first adjusting the value of c in Equation 2.8 so that the resulting phase noise at large offsets matches the simulated value (since the phase noise at large offsets will be dominated by white noise and c describes only the white noise component in the model). Once the phase noise at large offsets matches then the amount of flicker noise can be adjusted using  $c_f$  to match the shape of the phase noise curve at lower frequency offsets. The end result is that the discrete time sequence produced by Equation 2.8 with the two adjusted constants produces a waveform that has the same phase noise properties as that predicted by a circuit level simulation of the real oscillator. An example power spectral density and the cycle-to-cycle frequency variation after down-conversion to IF are shown in Figure 2.6. Depending on the time scale of observation relative to the level of flicker noise, the histogram of cycle-to-cycle frequency may no longer be Gaussian. The flicker noise essentially causes the mean frequency after down-conversion to wander. If this mean wander is slow compared to the duration of a packet, then the receiver will perceive it as a center frequency error with the cycle-to-cycle variation being predominately due to white noise. The MATLAB script for generating a time domain sequence of the noisy oscillator in Figure 2.6 is given in Appendix A.

$$\phi(k) = 2\pi f_0 \cdot (\sum_{n=0}^{k-1} w(n)\sqrt{c\Delta t} + \Delta t \sqrt{2\pi c_f}) \sum_{n=0}^{k} (h_{k-n} \cdot w_f(n))$$

(2.8)

Figure 2.7: Block diagram of the main components of the received used to develop the initial performance model.

# 2.3 Receiver Design and Modeling

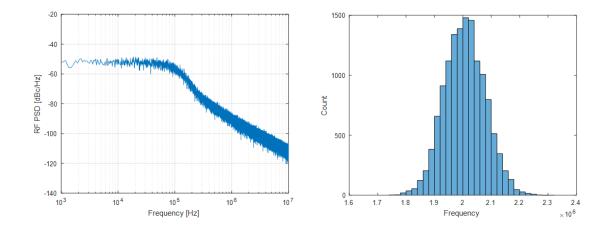

Based on the decisions outlined earlier in this chapter a block diagram of the receiver to be modeled is shown in Figure 2.7. The receiver will use a free-running quadrature LO to down-convert to a low IF. Gain, filtering, and digitization will be implemented on-chip and both types of demodulators introduced previously will be implemented. There are many interdependent parameters to be determined which affect the trade-off between the overall performance of the receiver and its power consumption. In order to reduce the complexity of the design space the error rate performance will first be assessed only in the presence of noise sources within the receiver. The design can then be extended to consider the effects of interference and how to meet the standard requirements.

At this stage it is difficult to set concrete design limits on the power consumption of the receiver without knowing more about the required circuit performance. However some information is available from previous hardware generations which can serve to provide the basis for a rough estimate. The LC local oscillator in [27] consumed 1 mW of power. Its performance appeared to be substantially better than required for implementing an 802.15.4 receiver so it was assumed to be possible to reduce this power. However that design did not include on-chip biasing and supply regulation so its performance is likely to change once those circuits are integrated. This work is not concerned with the circuit design details of the LO (see [17]) but at the time that the receiver design began it seemed reasonable to assume that the LO power could be reduced by at least a factor of two to 500  $\mu W$ . It was also known from previous hardware measurements that the Cortex-M0 operating at 5 MHz consumed 250  $\mu W$ . This power consumption did not include any of the digital baseband circuitry which now must be added (Chapter 4). Assuming that the digital baseband at most doubles the digital power consumption, and that the analog portion of the radio including both the LO and the rest of the receiver can be limited to less than 1 mW, the total power consumption in receive mode would be somewhere between 1 and 1.5 mW.

To assist in the design and verification of the receiver it is very useful to have a behavioral model that mimics the functionality of the real receiver and includes various non-idealities. There is a trade-off here between how much depth and detail is implemented in the model versus how much time investment it takes to implement the modeling. On one hand a very

detailed simulation that takes into account the complete receiver and all known non-idealities increases the likelihood that problems will be caught before tape-out. On the other hand though one could spend forever modeling and verifying and never actually end up taping anything out. The designer must decide how to find the appropriate balance with the obvious goal being to reach working silicon as quickly as possible. There are many ways to go about modeling a transceiver: MATLAB, Verilog-A, as well as many commercial system simulator packages like Simulink or SystemVue. Each option has its advantages and disadvantages. System modeling packages allow a designer to implement rather complex models quickly using a building block approach, but this can remove the requirement that the designer actually understands what is going on inside these blocks. Implementing each of these blocks from the ground up in MATLAB forces the designer to gain an understanding of how each subsystem works. Verilog-A has the advantage of tight integration with the circuit simulator environment so that idealized model blocks can be replaced with real circuit implementations to assess their impact on the model performance. For this work MATLAB was chosen mostly for its flexibility and ability to implement blocks from the ground up, although Verilog-A also looks very attractive if this design were to be repeated from the beginning. Regardless of the simulation method chosen the process is going to be iterative as ideal blocks are replaced with more realistic representations and requirements are re-evaluated.

#### Choosing an Intermediate Frequency

There are many things to consider when choosing what IF to down-convert to. matched filter templates are implemented as sine and cosine waves of the two MSK tones that the transmitter alternates between (see Section 4.1). Convolution of these templates with the incoming signal acts like a bandpass filter around each frequency tone. The lowest frequency of which a full cycle can be captured in the 500 ns chip duration is 2 MHz. The consequence being that templates for frequencies lower than this will implement a low pass filter rather than a bandpass which will have some impact on performance which must be modeled. The choice of IF also has an impact on the deviation caused by phase noise as seen in Equation 2.5, but as will be discussed shortly, the impact of phase noise overall is minimal so this is not of great concern. The power consumption of analog filters is dependent on the bandwidth they must achieve. By moving to a higher IF, the amplifiers in the filter will need to become faster and thus consume more power. Flicker noise in the analog portion of the receiver must be carefully managed if a very low IF is considered, although this could be mitigated by using large devices in layout or using techniques such as chopping and double correlated sampling. For the ZCC demod a low IF is again preferred as it maximizes the frequency ratio between the two FSK tones for a fixed tone spacing. The preceding constraints all point to a low IF possibly located in the single digit MHz range. Given this set of considerations an initial choice of an IF of 2.5 MHz was chosen for the system modeling going forward. This is the lowest choice for which the matched filter templates will still contain an entire cycle of the 2 MHz and 3 MHz tones that result from the choice of 2.5 MHz. This value could be revisited as the model is refined and circuit implementations are solidified, although it remained satisfactory throughout the SCM design phase. No detrimental side effects of this choice were discovered during modeling and no obvious better choice was found.

#### Receiver Noise Sources

The main source of thermal noise within the receiver is the circuit noise added by the RF frontend. Additional noise will also be added from other downstream circuitry and collectively the total amount of noise is captured in the design metric known as noise figure. The required receiver sensitivity of -85 dBm, the chosen filter bandwidth of 2 MHz, and the noise figure are related by Equation 2.9. The remaining unknown term is the minimum amount of SNR required at the demodulator input to achieve the specified 1% packet error rate. The SNR requirement can be derived from a system level model which will then allow a minimum noise figure to be calculated.

$$-174dBm + 10log10(2e6) + NF + SNR_{min} = -85dBm$$

(2.9)

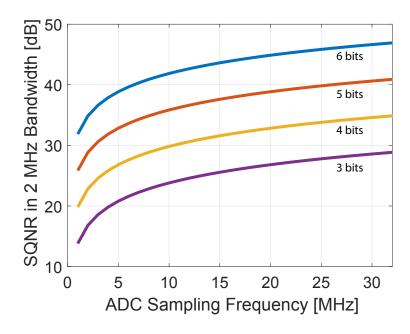

In addition to amplifier noise, ADC quantization noise also contributes to in-channel degradation of the SNR. High performance receivers generally use a large enough number of bits that the quantization noise floor is much lower than the thermal noise floor. The number of bits chosen for the ADC presents an opportunity for trading off power and performance. Using more bits increases both the dynamic range and the achievable SNR but is also more costly in terms of power, both for the ADC itself and also the following digital baseband. The SNR requirements for a demodulator are generally quite modest in comparison to the SNR achievable by an ADC even with only a few bits. The required dynamic range depends on how much interference must be tolerated at the input to the ADC. An ADC with a large number of bits is able to digitize the desired signal alongside other larger signals and then filter out the interference digitally. Given the interference requirements for IEEE 802.15.4, it is assumed here that any unwanted signals present have been sufficiently filtered prior to the ADC so that their amplitude is less than or equal to the desired channel. This allows the dynamic range requirements to be relaxed and a smaller number of bits can be used for the ADC to save power.

ADC sampling rate affects the quantization noise density as well as interference folding. Oversampling is beneficial in both cases as it reduces the in-band noise density and relaxes the requirements for anti-aliasing prior to the ADC. The signal can always be down-sampled at a later stage to reduce power consumption if desired. The trade-offs between sample rate, the number of bits, and the achievable SNR considering only quantization noise are shown in Figure 2.8. This plot assumes that a digital channel select filter has been used to band-limit the noise to the same 2 MHz bandwidth as was chosen for the signal filter. It can be seen that SQNR in excess of 20 dB is easily achieved and thus quantization noise is not likely to be a substantially limiting factor even for ADCs with small numbers of bits.

Figure 2.8: The achievable signal to quantization noise ratio for a given sampling frequency and number of bits when the signal is digitally band-limited to 2 MHz.

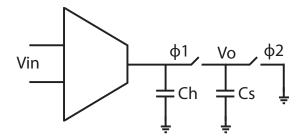

The matched filter demodulator and CDR require an integer number of samples per symbol in order to perform their respective functions. This translates to the requirement that the ADC clock rate is an integer multiple of the chip rate of 2 MHz. Furthermore the algorithm used for CDR, discussed in Chapter 4, requires a power of two for the number of samples per symbol. This effectively reduces the choices for ADC sampling rate to 8, 16, or 32 MHz. The choice is ultimately driven by a trade-off between power consumption and where interference aliases to after being sampled. Considering these trade-offs, a frequency of 16 MHz is used for the ADC clock in the system level modeling to follow. The source of the ADC clock should also be taken into account from both a tuning and jitter perspective. While the clock jitter is generally only a problem when targeting SNR values far in excess of those discussed here, the derivation of the chip clock from this source means that its tuning accuracy is quite critical. For initial modeling this clock is assumed to be ideal and these issues will be discussed further in Chapters 3 and 4.

The zero crossing counter demod requires a much higher sample rate due to its attempt to measure the time between zero crossings. A high speed clock is needed to ensure the difference between high and low FSK tones can be distinguished. Using too high of a clock speed is also undesirable from a power perspective as the comparator output bit stream must be processed by the digital implementation of the zero crossing demod. A first estimate about what clock rate to use is chosen to be bounded by 50 MHz on the low end and 100 MHz as the upper speed limit. A third intermediate value of 76 MHz is also added as another data point. Since the 2 MHz chip rate is recovered from the same clock that operates the

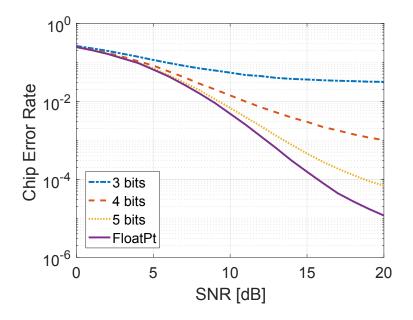

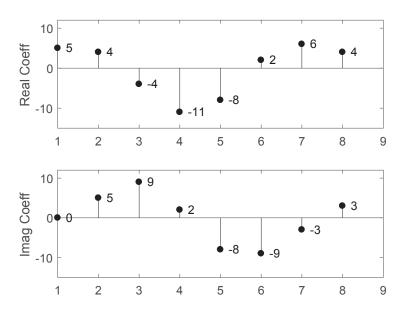

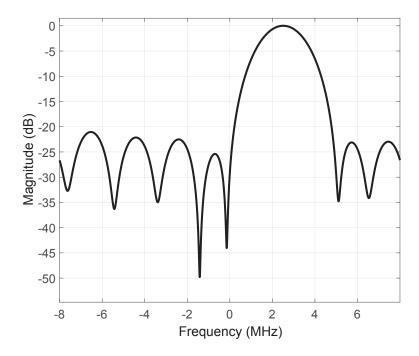

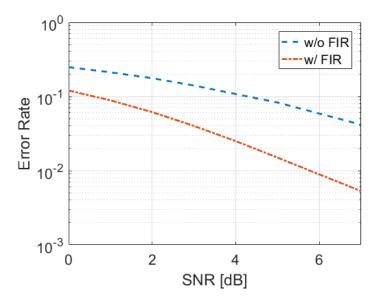

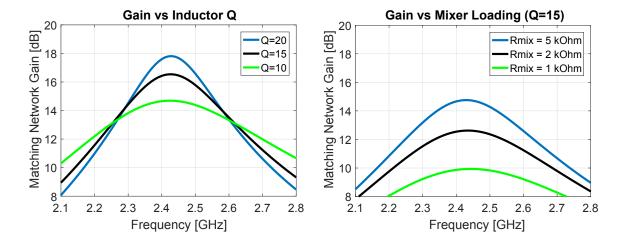

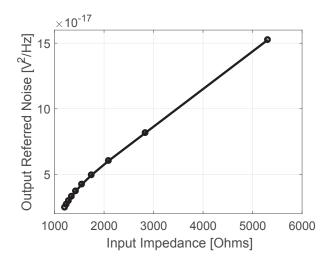

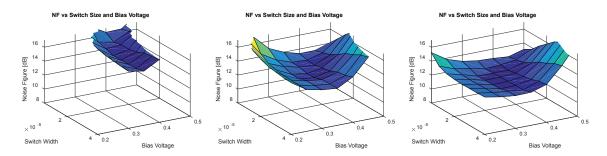

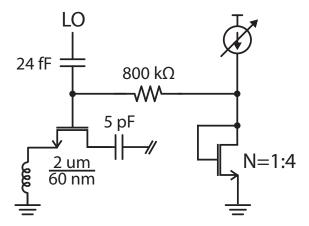

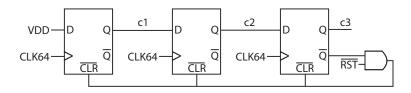

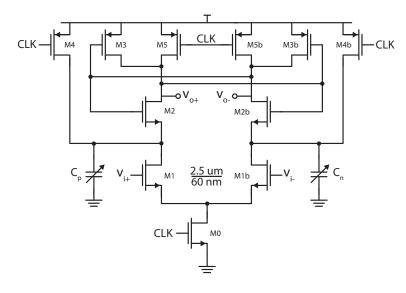

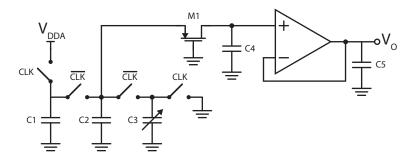

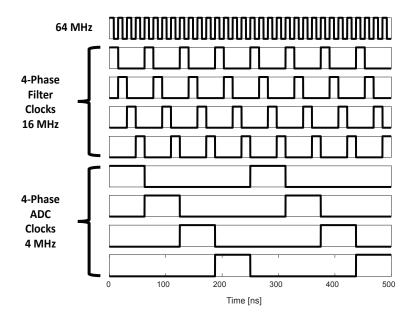

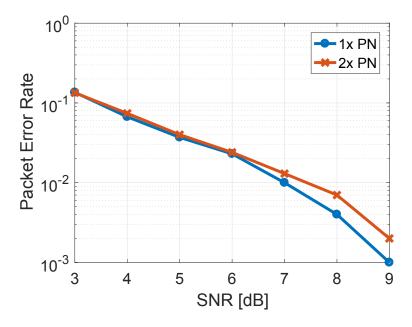

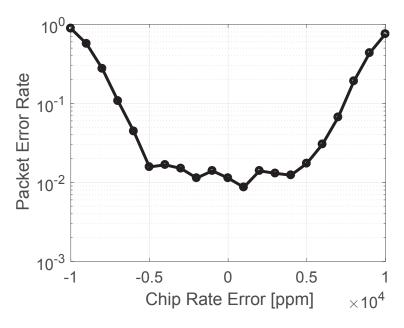

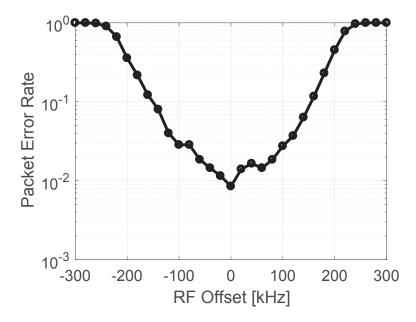

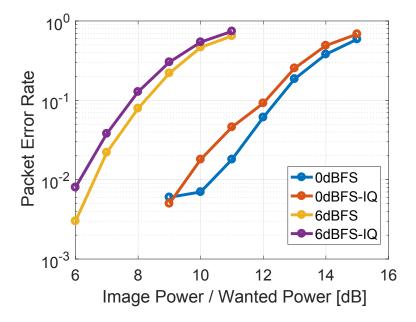

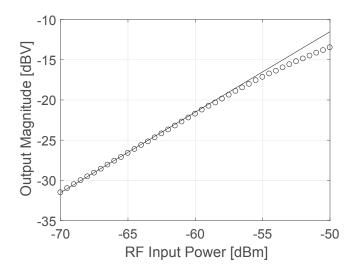

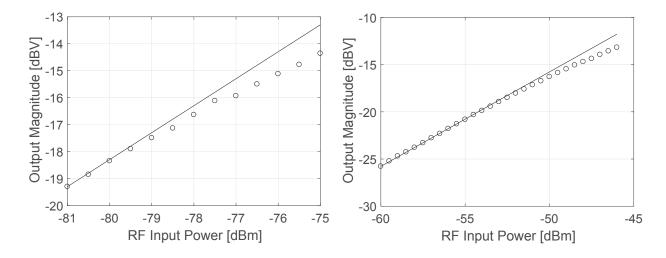

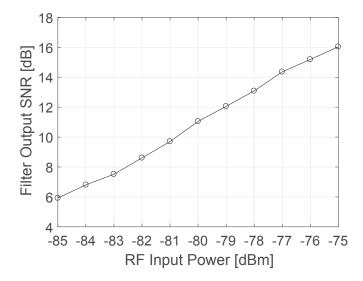

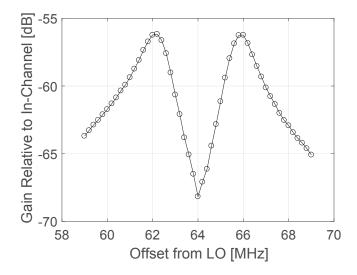

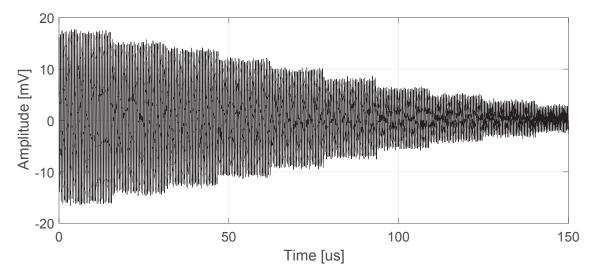

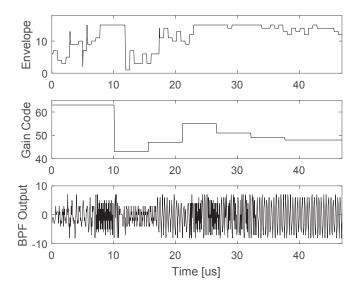

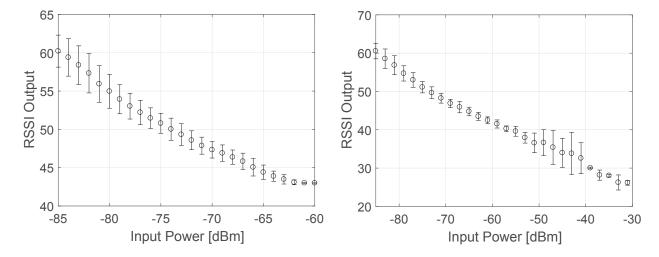

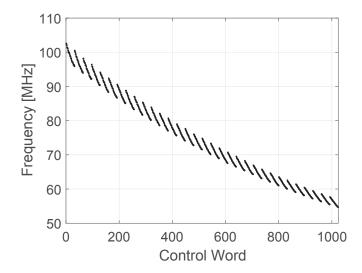

demodulator, the clock rate must be a multiple of two and thus 75 MHz is rounded up to 76 MHz.